第六章单元测试

- 一个容量为1K×8的存储器有( )个存储单元

- 要构成容量为4K×8的RAM,需要( )片容量为256×4的RAM。

- 寻址容量为16K×8的RAM需要( )根地址线。

- 若RAM的地址码有8位,行、列地址译码器的输入端都为4个,则它们的输出线(即字线加位线)共有( )条。

- 某存储器如图所示,

该存储器的容量为( )。 - 采用对称双地址结构寻址的1024×1的存储矩阵有( )

- 欲将容量为128×1的RAM扩展为1024×8,则需要控制各片选端的辅助译码器的输出端数为( )

- RAM的结构如图所示,

如输入地址代码A7A6A5A4A3A2A1A0=11110000,则行选线X0=1、列选线Y15=1,选中第X0行第Y15列的那个存储单元。( ) - PROM的或阵列(存储矩阵)是可编程阵列。( )

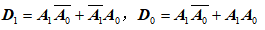

- 电路如图所示

D1和D0的逻辑表达式为

D1和D0的逻辑表达式为 ( )

( )

A:8

B:8000

C:8192

D:10K

答案:8192

A:2

B:8

C:4

D:32

A:16K

B:16

C:4

D:14

E:8

A:32

B:256

C:16

D:8

A:4K×5

B:6K×8

C:5K×8

D:4K×8

A:5行5列

B:32行32列

C:10行10列

D:1024行1024列

A:1

B:8

C:2

D:3

A:对 B:错

A:对 B:错

A:错 B:对

温馨提示支付 ¥3.00 元后可查看付费内容,请先翻页预览!