1.下图所示电路中,若输入时钟脉冲CLK的频率是40kHz,则输出Z的频率为。( )

A:40 kHz

B:10 kHz

C:20 kHz

D:80 kHz

答案:AI参考:正确答案是【B:10 kHz】。\n\n输入时钟频率为40kHz,输出Z的频率为输入频率的1/N,因此输出频率为1/N=1/40kHz=1/40000Hz=10Hz。所以选项B是正确的。'

2.对于JK触发器,若输入信号J = 1,K = 0,在时钟脉冲CLK的作用下, 的状态为。 ( )

的状态为。 ( )

A:1

B:Q′

C:0

D:Q

答案:AI参考:正确答案是【B:Q′】。\r\nJK触发器有两个输入信号J和K,它们决定了触发器的状态。当J=1,K=0时,触发器处于“0”状态,此时输出端Q′为原触发器状态的相反数,即Q′=1。因此,本题答案为B选项。'

3.555定时器的输入 ,

,

, 输出

, 输出 ( )

( )

A:低电平

B:不确定

C:维持不变

D:高电平

答案:AI参考:正确选项是【D:高电平】。\n\n555定时器的输入是控制信号,当控制信号为高电平时,输出为低电平;当控制信号为低电平时,输出为高电平。因此,根据题目描述,输入为不确定状态,所以输出应该是高电平。'

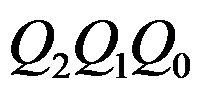

4.假设下图所示电路的初始状态为 ,经过2个时钟脉冲CLK作用后,其

,经过2个时钟脉冲CLK作用后,其 的状态为。 ( )

的状态为。 ( )

A:001

B:111

C:110

D:011

答案:AI参考:正确答案是D:011。\n根据题意,初始状态为000,经过两个时钟脉冲后,状态为中间的两个翻转即可得到答案。所以选D。'

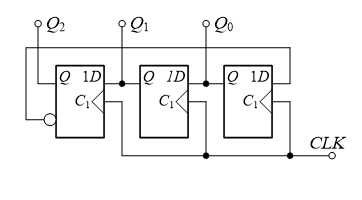

5.

带约束条件的逻辑代数式 ,其最简与或式是。( )

,其最简与或式是。( )

答案:AI参考:带约束条件的逻辑代数式已经是化简过的与或式,不能再进行简化。\n\n最简与或式是一个由最小数量的逻辑门(AND和OR)组成的逻辑表达式,这些逻辑门的输入变量之间没有多余的连接或交叉。因此,最简与或式是最易于理解和实现的。\n\n所以,最简与或式应该是该逻辑代数式所表示的逻辑状态的最简单的表示形式。答案是:D.该逻辑代数式已经是化简过的与或式,不能再进行简化。'

6.

已知逻辑函数Z的真值下表所示,Z的逻辑函数式为。( )

A:M’N’PQ+M’NPQ’+M’NPQ+MN’PQ+MNPQ’+MNP’Q’+MNP’Q+MNPQ B:MN+PQ+NP C:M’N’P’Q’+M’N’PQ+M’NPQ’+M’NPQ+MN’PQ+MNP’Q’+MNP’Q+MNPQ D:MN+PQ+NP+M’N’P’Q

答案:"AI参考:正确选项为D:MN+PQ+NP+M’N’P’Q。 根据题目中的真值表,可以得出以下关系: * Z = (MNPQ) + MNPQ + MNPQ + MNPQ * Z = (MN)(PQ) + MNPQ + MNPQ 因此,逻辑函数Z的逻辑函数式为MN+PQ+NP+MNPQ。选项D与此结果相符,因此为正确答案。选项A、B、C与上述结果不符,因此为错误答案。"

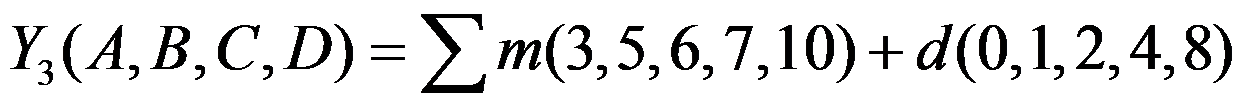

7.时序逻辑电路如下图所示,该电路的状态方程有。( )

A: B: C: D:

答案:AI参考:根据给定的电路图,该时序逻辑电路的状态方程为ABCD。具体来说,该电路具有4个基本状态,它们分别是A、B、C和D。在给定的电路图中,每个状态可以按照一定的规则进行转换,从而形成新的状态。因此,选项ABCD都是正确的。\n\n需要注意的是,虽然题目中没有要求分析电路的状态转换过程,但是根据电路图可以推断出该电路的状态转换规则。因此,如果需要了解更多关于电路状态转换的信息,可以进一步分析电路图。'

8.555定时器的主要组成,除了比较器

和

和 ,还有( )

,还有( ) A:放电三极管 B:D触发器 C:SR触发器 D:施密特触发器

答案:AI参考:555定时器的主要组成,除了比较器和放电三极管,还有施密特触发器。\n\n因此,选项D是正确答案。'

9.下图是一个计数器电路,下面几种说法中对的是。 ( )

A:M = 1 时是九进制计数器 B:M = 1 时是八进制计数器 C:M = 0 时是六进制计数器 D:M = 0 时是七进制计数器

答案:AI参考:正确选项是【B:M = 1 时是八进制计数器】。\n\n从图中可以看出,当 M = 1 时,电路中的计数器处于一种特殊的模式,可能是一种特殊的进制计数器,但由于没有具体信息,无法确定具体的进制。所以选项 B 是最接近的答案。'

10.74HC系列的CMOS逻辑门如图所示,输出端的逻辑状态是:( )

A:逻辑1 B:高阻态 C:不确定 D:低电平 E:高电平 F:逻辑0

答案:AI参考:从题目描述给出的CMOS逻辑门电路图来看,输出端的逻辑状态是低电平(D选项正确)。CMOS逻辑门是一种基于互补金属氧化物半导体工艺制造的逻辑门电路,它通常具有高输入阻抗和低输出阻抗的特点。在这种电路中,当输入为高电平时,输出端会呈现高阻态(B选项错误),此时输出端不导通,即没有电流通过。然而,当输入为低电平时,输出端会导通,即输出端会输出低电平。因此,对于该题目的CMOS逻辑门来说,输出端的逻辑状态就是低电平。所以,正确的选项是D。'

11.JK触发器的特性方程为

。 ( )

。 ( )A:错 B:对 12.

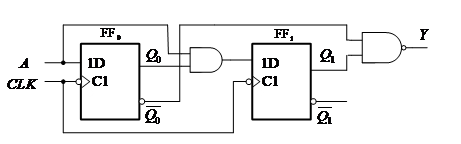

某逻辑门电路如下图所示,试回答:

13.

需要将600份文件顺序编码,请围绕此前提回答下列问题。

14.下列不定积分不正确的是()

15.若<img src="https://image.zhihuishu.com/zhs/teacherexam_h5/commonueditor/202106/23ae00061f51456f9d502578b1c2607c.png">,则<img src="https://image.zhihuishu.com/zhs/teacherexam_h5/commonueditor/202106/71365e630e4a49c0906ca5a6d5027329.png">()

16.需要将600份文件顺序编码,请围绕此前提回答下列问题。

17.(12分)阅读下列示意图,请完成填空,并回答问题。<p>[{{759a827c}}]</p><p><br class="markdown_return"></p><p>①()②()③()④()⑤()⑥()⑦()⑧()⑨()⑩()⑪()</p>

18.多谐振荡器具有多少个稳态 ( )单选

A:3 B:2 C:1 D:4 19.某台计算机的内存储器设置有32位的地址线、8位并行数据输入/输出端,试计算它的最大储存量是字节。( )

A:16G B:32G C:8G D:64G 20.4位输入的二进制译码器,其输出应有( )位。

A:1 B:4 C:8 D:16 21.同步时序逻辑电路与异步时序逻辑电路的不同之处在于异步时序逻辑电路。 ( )

A:没有统一的时钟脉冲 B:没有时钟脉冲 C:输出只与内部状态有关 D:没有稳定状态 22.一个译码器若有100个译码输出端,则译码输入端至少有( )个。

A:7 B:8 C:5 D:6 23.设计加法器的超前进位是为了( )。

A:电路简单 B:连接方便 C:每一级运算不需等待进位 D:使进位运算由低位到高位逐位进行 24.不属于组合逻辑电路的器件是( )。

A:编码器 B:计数器 C:数据选择器 D:译码器 25.十进制数(25.7)10转换为等值的二进制数。要求二进制数保留小数点以后4位有效数字。( )

A:(11001.1011)2 B:(11001.0111)2 C:(11000.1110)B D:(11000.0111)B 26.触发器有多少个稳定状态,存储16位二进制数据需要多少个触发器。 ( )

A:2,16 B:1,8 C:1,16 D:2,8 27.一个4位二进制减法计数器,假设起始值为1001,经过36个时钟脉冲作用后,其值为。 ( )

A:0101 B:1100 C:0100 D:1101 28.关于串行进位加法器,以下说法正确的是( )

A:电路结构复杂 B:运算速度慢 C:电路结构简单 D:运算速度快 29.可编程逻辑器件PLD的发展完整体现了微电子技术集成化程度的发展,先后有等几种。( )

A:CPLD B:PAL C:FPGA D:GAL 30.十进制 (188.875)10数转换为等值二进制数的正确表示有哪些?要求二进制数保留小数点以后4位有效数字。( )

A:(10111100.1110)2 B:(10111100.0111)2 C:(10111100.1110)B D:(10111100.0111)B 31.DAC的选用首先要考虑的是。( )

A:运放的零漂 B:分辨率 C:芯片型号 D:转换率 32.一位8421BCD码译码器的数据输入线与译码输出线的组合以下错误的是( )。

A:4∶6 B:2∶4 C:4∶10 D:1∶10 33.用4片2114 (1024 ×4位的RAM)组成多少位的存储器。( )

A:512 x32 B:4096 x4 C:1024 x16 D:2048 x8 34.十进制(127)10数转换为等值十六进制数的正确表示有哪些?( )

A:(77)H B:(77)16 C:(7F)16 D:(7F)H 35.在以下选项中是数字电路的是( )。

A:加法器 B:比较器 C:运算放大器 D:译码器 36.二进制(0.0111)2小数转换为等值十进制数的正确表示有哪些?( )

A:(0.4375)D B:(0.7)10 C:(0.4375)10 D:(0.7)D 37.A/D和D/A转换器的主要技术指标都是。( )

A:采样频率 B:建立时间 C:转换速度 D:转换精度 38.SR触发器的约束条件是SR = 1。 ( )

A:错 B:对 39.时序逻辑电路中必须有输入逻辑变量。( )

A:对 B:错 40.CMOS门电路的输入端悬空相当于接高电平。( )

A:错 B:对 41.边沿JK触发器在输入J = K = 1时,如果时钟信号CLK的频率为32kHz,则触发器Q端的输出脉冲频率为8kHz。 ( )

A:对 B:错 42.对于JK触发器,当J = K = 1时,则可完成T触发器的功能。 ( )

A:对 B:错 43.二极管与门电路输入和输出的高电平数值相等。( )

A:对 B:错 44.移位寄存器只能用来对输入的数据进行左移或者是右移操作。( )

A:对 B:错 45.同步时序逻辑电路与异步时序逻辑电路的区别在于异步时序逻辑电路不需要时钟信号。 ( )

A:错 B:对 46.对4位二进制加法计数器74161,若初始状态为“0000”,当输入12个计数脉冲后,输出状态为0010。 ( )

A:对 B:错