中国农业大学

- https://image.zhihuishu.com/zhs/doctrans/docx2html/202008/3495f5eb5dc344ed9e5f0837472dcec6.png

- https://image.zhihuishu.com/zhs/doctrans/docx2html/202008/07be98b923874a1086de70cac4b5bf08.png

- 用3线-8线译码器74HC138和门电路,设计1位二进制全减器电路。输入为被减数、减数和来自低位的借位;输出为得到的差及向高位的借位信号。

- 将具有无关项的逻辑函数化为最简的与或逻辑式: Y(A,B,C,D)=∑m(2,3,7,8,11,14)+d(0,5,10,15)

- 数制转换: ⑴ 将下列十六进制数转换成等值的二进制数:(3D.BF)16 ⑵ 将下列十进制数转换成等值的二进制数和十六进制数:(188.875)10

- https://image.zhihuishu.com/zhs/doctrans/docx2html/202008/9250ee9dacf846e88ec841a87f6c45ef.jpeg

- 主从结构的脉冲触发器的状态转换图描述的是其中“主触发器”的状态。( )

- 施密特触发电路有两个能自行保持的稳定状态。 ( )

- 时序逻辑电路的结构当中一定含有存储电路。( )

- 在各种电路结构的A/D转换器中,逐次渐进性A/D转换器的转换速度最快。( )

- 触发器的基本要素是能够写0/1,且在下次写入前保持0/1。( )

- PLA的基本电路结构是一个可编程的与逻辑阵列和一个可编程的或逻辑阵列。( )

- 3线-8线译码器74HC138,其每一个输出都是三变量逻辑函数的一个最小项的非,所以它也被称为最小项译码器。( )

- 二值逻辑中,每个变量的0和1用来表示两种不同的逻辑状态。 ( )

- 只有与-或形式的逻辑函数式才能化成最小项之和的形式。( )

- 存储衡量存储器性能的指标不包括存储速度( )

- SR触发器的约束条件是S和R的取值不能同时为有效信号( )

- PLD在生产时按通用器件生产,使用时用户可对其编程来实现所需的逻辑功能。 ( )

- 对在系统可编程逻辑器件进行编程时,需要使用专门的编程器。( )

- 集电极开路的与非门和普通的与非门,他们的逻辑功能相同,使用方法也完全相同。( )

- 硬件描述语言Verilog HDL 中,wire语句用来定义reg 类型的变量。( )

- 在一个触发脉冲内,可以确定所存储的数据Q只变化一次的是( )

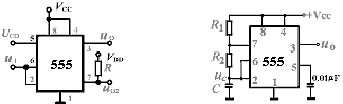

- 下图为555定时器的应用电路,该电路把555定时器接成_________。 ( )

- 用6个触发器,最多可构成多少进制的计数器? ( )

- 若一个ROM有10位地址线,8位数据线,则它的存储容量有多大?( )

- 石英晶体振荡器的输出频率取决于? ( )

- 关于FPGA,你认为: ( )

- 下列哪个函数是最小项之和的形式?( )

- 同步计数器和异步计数器比较,异步计数器的最显著优点是( )

- 要将正弦信号转换成与之频率相同的矩形脉冲信号,应采用? ( )

- 逻辑函数的所有最小项之和等于? ( )

- 下图中的门电路是74系列TTL电路。试问门电路的输出是什么状态? ( )

- 用( ) 电路构成模为16的计数器的译码逻辑最简单.( )

- 以下各种A/D转换器电路类型中,转换时间与输入电压大小无关的是哪种? ( )

- 欲使JK触发器按Q* =Q′工作,可使JK触发器的输入端 ( )。

- 某存储器有20根地址线,有8根平行数据线,则该存储器的最大存储容量为________ ( )

- 以下哪种电路在任何时刻,只有一个输出端有效。 ( )

- 要对298个物体进行编码,下面那个选项可以实现? ( )

- 相对于CMOS电路来说,TTL电路的优点是: ( )

- 要用T触发器构成10进制计数器,最少需要用( )个触发器。( )

- 数字信号是指________。 ( )

答案:

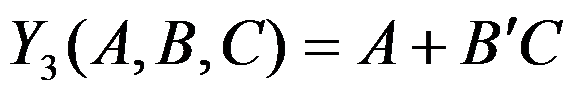

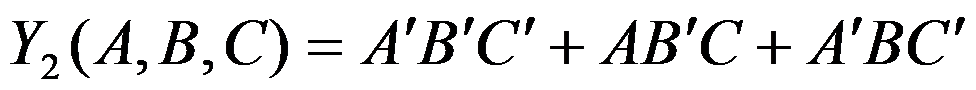

答案:

答案:使用74HC138 3线-8线译码器和门电路设计的1位二进制全减器电路,其输入包括:A(被减数),B(减数),Ci(来自低位的借位)。输出包括:D(差),Co(向高位的借位信号)。具体电路设计如下: 1. 将A、B、Ci连接到74HC138的地址输入端A0、A1、A2,以生成基于这三个输入的8种可能组合的译码输出。 2. 使用与门(AND gate)和或门(OR gate)来组合74HC138的输出,以计算差D和向高位的借位Co。 具体门电路连接方法简述如下(未提供真值表,直接依据全减器逻辑构建): - Co = (A'BCi) + (AB'Ci) + (ABC'i) // 使用3个与门和一个或门实现 - D = A'B'Ci + A'BC'i + ABC'i // 使用与门实现,注意这里的D实际是求被减数A与减数B及借位Ci异或的结果后,根据Co进行修正的结果。但直接表述逻辑可能略显复杂,实际应用中需考虑借位逻辑对最终差值D的影响,此处简化表述主要关注输出逻辑构造。 注意:上述逻辑表达式简化了实际设计中的逻辑处理,特别是D的计算需要考虑借位逻辑与差值计算的综合影响,实际实现时可能需要更复杂的门电路组合来准确反映全减器的功能。在实际电路设计中,还需细致规划每个输出如何通过特定的与门、或门组合来正确反映全减器的逻辑行为。

答案:略

答案:⑴ (3D.BF)16 转换为二进制: 3D: 0011 1101 BF: 1011 1111 所以,(3D.BF)16 = (0011 1101.1011 1111)2 ⑵ (188.875)10 转换为二进制和十六进制: 二进制: 188: 1011 1000 0.875: 0.111 因此,(188.875)10 = (1011 1000.111)2 十六进制: 188: BC 0.875 转换为十六进制需要先转换为二进制小数,已知0.875对应二进制小数0.111,即0.875 = (111)2 * 2^-3 = (0.111)2,直接计算可能不直观,但根据二进制到十六进制的转换规则,每四位二进制转换为一位十六进制,0.111没有前导0,可以理解为0001.1100,因此是0.1C。 所以,(188.875)10 ≈ (BC.1C)16 (注意,十六进制中小数点后的转换可能存在近似处理,实际中0.875转为十六进制更精确地应考虑四舍五入或特定转换规则)

答案:

A:错 B:对

答案:错

A:错 B:对

答案:错

A:对 B:错

答案:对

A:错 B:对

A:错 B:对

A:对 B:错

A:对 B:错

A:错 B:对

A:错 B:对

A:错 B:对

A:对 B:错

A:错 B:对

A:错 B:对

A:对 B:错

A:错 B:对

A:基本RS锁存器 B:电平触发的RS触发器 C:主从RS触发器

A:施密特触发器 B:多谐振荡器 C:单稳态触发器 D:计数器

A:6进制 B:64进制 C:12进制 D:36进制

A:2048 B:80 C:4096 D:1024

A:电阻、电容的参数及石英晶体的固有频率 B:电阻、电容的参数 C:石英晶体的固有频率 D:无法确定

A:只能实现组合逻辑电路 B:组合、时序逻辑电路,均能实现 C:只是一个软件程序,不能实现任何电路 D:只能实现时序逻辑电路

A:

B:

B: C:

C: D:

D:

A:B.触发器利用率高 B:工作速度高 C:D.无竞争冒险现象 D:C.电路简单

A:移位寄存器 B:单稳态触发电路 C:施密特触发电路 D:多谐振荡电路

A:0或1 B:0 C:1 D:任意值

A:高电平; B:低电平; C:无法确定

D:高阻抗;

D:高阻抗;

A:环形计数器 B:同步计数器 C:异步计数器 D:扭环形计数器

A:无法确定 B:双积分型; C:计数型; D:逐次渐近型;

A:J= Q′,K=Q B:J= K=1 C:J=Q,K=Q′ D:J=K=0

A:1 M B:1M×8 C:1K×8 D:20×8

A:十进制计数器 B:七段显示译码器 C:二进制编码器 D:二进制译码器

A:9位二进制数 B:两位十进制数 C:两位八进制数 D:两位16进制数

A:速度快 B:集成度高 C:功耗小 D:电源电压有一个宽的使用范围

A:2 B:4 C:6 D:8

A:时间上离散的信号 B:数值上离散的信号 C:时间上和数值上都离散的信号 D:时间上和数值上都连续的信号

温馨提示支付 ¥5.00 元后可查看付费内容,请先翻页预览!