第三章测试1.组合逻辑电路中的冒险是由于( )引起的。

A:电路有多个输出 B:逻辑门类型不同 C:电路未达到最简 D:电路中的时延

答案:D

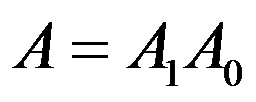

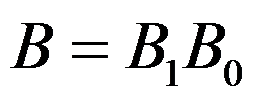

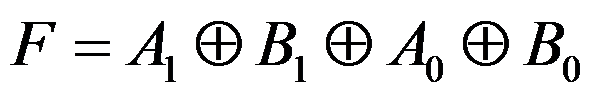

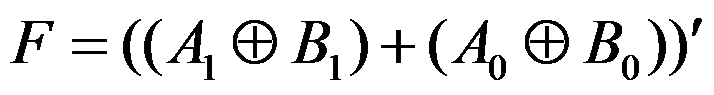

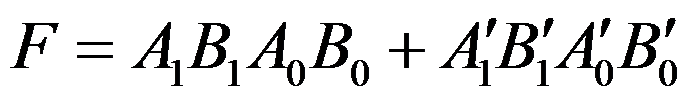

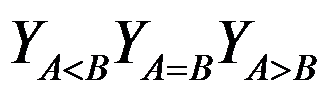

2.比较两位二进制数

和

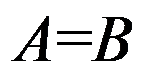

和 ,当

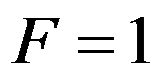

,当 时输出

时输出 ,则F表达式是( )。

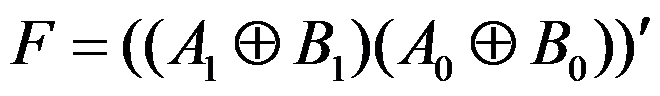

,则F表达式是( )。 A:

B:

B: C:

C: D:

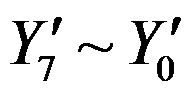

D: 3.3线-8线译码器74HC138处于译码状态时,当输入A2A1A0为101时,输出

3.3线-8线译码器74HC138处于译码状态时,当输入A2A1A0为101时,输出 为( )。

为( )。 A:11011111 B:00000101 C:00100000 D:11111011 4.数据分配器和( )有着相同的基本电路结构形式。

A:编码器 B:加法器 C:数据选择器 D:译码器 5.集成4位数值比较器74HC85级联输入IAB为分别接001时,当输入两个相等的4位数据时,输出

分别为( )。

分别为( )。 A:111 B:001 C:110 D:000 6.多位加法器采用超前进位的目的是( )。

A:提高运算速度 B:降低电路复杂度 C:提高运算精确度 D:其他选项都对 7.若两个最小项只有一个因子不同,则称这两个最小项具有( )。

A:相关性 B:相邻性 C:互补性 D:对偶性 8.组合逻辑电路任何时刻的输出信号,与该时刻的输入信号有关,与以前的输入信号无关。( )

A:对 B:错 9.能完成两个一位二进制数相加的器件称为全加器。( )

A:错 B:对 10.门电路两个输入信号同时向相反的逻辑电平跳变的一定会产生尖峰脉冲。( )

A:对 B:错

温馨提示支付 ¥3.00 元后可查看付费内容,请先翻页预览!