1.<img src="https://image.zhihuishu.com/zhs/onlineexam/ueditor/201910/dc31a71b0193489789b7ee6f5935210a.png">

答案:<img src="https://image.zhihuishu.com/zhs/onlineexam/ueditor/201910/9190be700d2746f5a727d25234170290.png">

2.<img src="https://image.zhihuishu.com/zhs/onlineexam/ueditor/201910/c64380507c99433d8d9244422914493f.png">

答案:<img src="https://image.zhihuishu.com/zhs/onlineexam/ueditor/201910/fa91ccc193114b0e8744312523e104c5.png">

3.<img src="https://image.zhihuishu.com/zhs/onlineexam/ueditor/201910/dc31a71b0193489789b7ee6f5935210a.png">

答案:<img src="https://image.zhihuishu.com/zhs/onlineexam/ueditor/201910/9190be700d2746f5a727d25234170290.png">

4.<img src="https://image.zhihuishu.com/zhs/onlineexam/ueditor/201910/c64380507c99433d8d9244422914493f.png">

答案:<img src="https://image.zhihuishu.com/zhs/onlineexam/ueditor/201910/fa91ccc193114b0e8744312523e104c5.png">

5.<img src="https://image.zhihuishu.com/zhs/onlineexam/ueditor/201910/dc31a71b0193489789b7ee6f5935210a.png">

答案:<img src="https://image.zhihuishu.com/zhs/onlineexam/ueditor/201910/9190be700d2746f5a727d25234170290.png">

6.<img src="https://image.zhihuishu.com/zhs/onlineexam/ueditor/201910/c64380507c99433d8d9244422914493f.png">

答案:<img src="https://image.zhihuishu.com/zhs/onlineexam/ueditor/201910/fa91ccc193114b0e8744312523e104c5.png">

7.<img src="https://image.zhihuishu.com/zhs/onlineexam/ueditor/201910/dc31a71b0193489789b7ee6f5935210a.png">

答案:<img src="https://image.zhihuishu.com/zhs/onlineexam/ueditor/201910/9190be700d2746f5a727d25234170290.png">

8.<img src="https://image.zhihuishu.com/zhs/onlineexam/ueditor/201910/c64380507c99433d8d9244422914493f.png">

答案:<img src="https://image.zhihuishu.com/zhs/onlineexam/ueditor/201910/fa91ccc193114b0e8744312523e104c5.png">

9.

答案:AI参考:很抱歉,您没有提供具体的阅读理解(选择)/完型填空问题或文本,因此我无法为您提供准确的答案。如果您能提供更多信息,我将很乐意帮助您解答。'

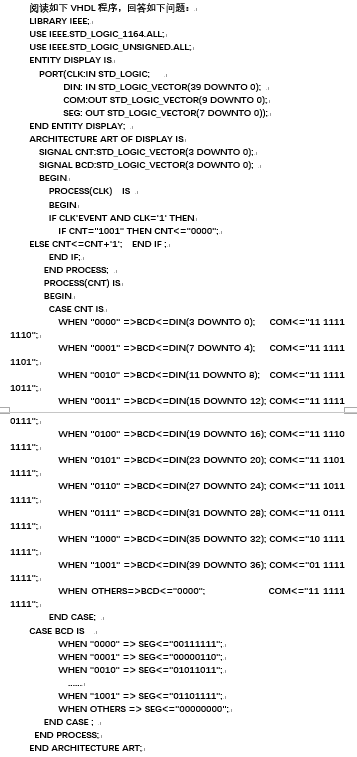

10.“LIBRARY IEEE;”表示该设计用到的库是( )库。

A:VITAL B:STD C:IEEE D:WORK

答案:IEEE

11.FPGA结构中的PIC(Program I/O Cell)的中文含义是( )

A:可编程I/O单元 B:可编程I/O细胞 C:可编程I/O元件 12. ASIC的中文含义是( )

A:复杂可编程逻辑器件 B:专用集成电路 C:在系统可编程特性 D:现场可编程门阵列 13.ASIC的英文全称是( )

A:Field Programmable Gate Array B:Electronic Design Automation C:Complex Programmable Logic Device D:Application Specific Integrated Circuits 14.“Complex Programmable Logic Device”的中文含义是( )

A:电子设计自动化 B:现场可编程门阵列 C:专用集成电路 D:复杂可编程逻辑器件 15.CAE的中文含义是( )

A:计算机辅助设计 B:计算机辅助工程设计 C:电子设计自动化 16.下列符号中表示与非的是( )

A:XNOR B:NOR C:ABS D:NAND 17.数据类型是标准逻辑位的选择项是( )

A:STD_LOGIC_1164 B:LOGIC C:STD_LOGIC_VECTOR D:STD_LOGIC 18.VHDL元件例化端口映射语句“U1:ND2 PORT MAP(A1,B1,S1); ”的端口映射关联方式为( )

A:结构关联 B:名字关联 C:混合关联 D:位置关联 19.语句含义为打开IEEE库的语句是( )

A:LIBRARY IEEE B:USE IEEE.STD_LOGIC_1164.ALL C:USE IEEE D:LIBRARY 20.CAD的英文全称是( )

A:Electronic Design Automation B:Computer Assist Engineering Design C:Computer Assist Design 21.语句“Y(0)<='1' WHEN SR="000" ELSE '0';”是一个( )

A:条件顺序信号赋值语句 B:条件执行信号赋值语句 C:条件并行信号赋值语句 22.一个具有 K 根输入线的 LUT 对应 ( ) bit 的存储器。

A:K2 B:K C:2K D:2的K次方,即2k 23.语句“R16S(6 DOWNTO 0)<=R16S(7 DOWNTO 1);”含义为( )

A:R16S(7 DOWNTO 1)的数据右移1位 B:R16S(7 DOWNTO 1)的数据左移1位 C:R16S(6 DOWNTO 0)的数据左移1位 D:R16S(6 DOWNTO 0)的数据右移1位 24.最流行的第三方EDA工具有:仿真功能最强大的是( )

A:ModelSim B:ispLEVER C:Quartus Ⅱ D:ISE/ISE-WebPACK Series E:Synplify 25.数字时钟管理器DCM主要包括的功能部分有( )

A:相位移位电路 B:延迟锁相环(DLL) C:状态逻辑 D:数字频率同步器(DFS) 26.Xilinx公司现有的FPGA产品( )

A:Spartan系列 B:Cyclone系列 C:Virtex系列 D:XC系列 27.开展本科生研究性教学的必要性有( )

A:提高大学生专业创新能力的需要 B:改变大学生被动学习学风的需要 C:提高大学生实践动手能力的需要 D:提高大学生专业综合素养的需要 E:大众化高等教育的差异化教育的需要 28.Cyclone Ⅲ器件平面结构的主要组成模块包括( )

A:嵌入式乘法器 B:嵌入式存储器块 C:I/O单元和PLL D:由逻辑阵列块(LAB) 29.逻辑宏单元(Macrocell)结构中的基本电路单元种类包括( )

A:选择器 B:寄存器 C:中央处理器 D:门电路 30.从应用和使用的角度讲,EDA技术的基本内容主要包括( )

A:硬件描述语言 B:实验开发系统 C:软件开发工具 D:大规模可编程逻辑器件 31.SOPC软件设计开发的基本步骤包括( )

A:启动设计工具Nios ⅡIDE B:将程序下载到FLASH存储器 C:运行程序或调试程序 D:建立新的源程序和软件工程或导入已建源程序和软件工程 E:编译工程 32.在 FPGA的发展历史上,出现过那些互连结构( )

A:层次化互联结构 B:孤岛型互联结构 C:通道型互连结构 33.PROCESS语句结构的组成包括( )

A:顺序描述语句部分 B:敏感信号参数表 C:进程说明部分 D:并行描述语句部分 34.IEEE_1076标准程序包中定义的四种常用端口模式是( )

A:FIFO模式 B:INOUT 模式 C:IN模式 D:OUT模式 E:BUFFER模式 35.Quartus Ⅱ的主要操作流程包括( )

A:工程仿真及分析 B:编程下载及验证 C:工程实现的设置 D:芯片的管脚锁定 E:文件及工程建立 F:工程编译及分析 36.通用EDA实验开发系统,就是指能够满足各种EDA实验或设计开发需要的EDA实验开发系统。

A:对 B:错 37.FPGA的英文全称是Field Programmable Gate Array。

A:对 B:错 38.反熔丝结构有两种:ONO 反熔丝和M2M 反熔丝。

A:对 B:错 39.顺序过程调用就是在顺序语句的环境中执行一个给定名字和参数的过程。( )

A:对 B:错 40.并行加法器通常比串行加法器占用更多的资源。

A:对 B:错 41.信号的使用和定义范围是实体、结构体和程序包。

A:错 B:对 42.信号赋值目标<= 赋值源;其中指向左边的双箭头(<=)作为一个整体,称之为信号赋值符号。

A:错 B:对 43.ASIC设计的版图设计(物理设计),就是是将逻辑设计中每一个逻辑元件、电阻、电容等以及它们之间的连线转换成集成电路制造所需要的版图信息。

A:错 B:对 44.为了使更多的VHDL设计实体能被方便地访问和共享,可以将我们已定义的常数、数据类型、元件调用说明以及子程序收集在一起,这就构成了VHDL程序包。

A:对 B:错 45.VHDL规定,已列出敏感量的进程中不能使用任何形式的WAIT语句。

A:对 B:错 46.功能仿真的结果与门级仿真器所做的功能仿真结果基本一致。

A:对 B:错 47.使用Altera的Quartus Ⅱ软件、SOPC builder/Qsys工具以及Nios Ⅱ集成开发环境IDE/Eclipse,用户可以轻松地将Nios Ⅱ处理器嵌入到FPGA系统,完成SOPC的硬件开发和软件开发。

A:对 B:错 48.一个文件夹下建立多个工程的方法是:从建第二个工程开始,当提示询问是否选择不同的工程目录时,选择“NO”,这时就可以在一个文件夹下建立多个工程。

A:错 B:对 49.并行简单信号赋值语句是VHDL并行语句结构的最基本的单元,它的语句格式如下:信号赋值目标<=表达式;

A:错 B:对 50.EDA技术可广泛应用于FPGA系统设计与开发、SOC/SOPC的设计开发、ASIC的前端设计等领域。

A:错 B:对 51.对于Quartus Ⅱ 10.0及其以上的高版本,除非安装了特定的Modsim-Altera仿真工具,可直接使用设置波形的形式进行仿真外,否则只能通过调用第三方仿真软件Modsim使用仿真测试程序的方式进行仿真。

A:对 B:错 52.进行ASIC设计的系统规格说明,就是分析并确定整个系统的功能、性能、物理尺寸;确定制造工艺、设计周期和设计费用;建立系统行为模型,进行可行性验证。

A:对 B:错 53.在大规模和超大规模逻辑资源、低功耗与价格比值方面,CPLD比FPGA有更大的优势。

A:错 B:对 54.七段数码管显示器可分为共阳极、共阴极型两种,其中共阴极型数码管是指数码管的7个发光二极管的阴极连接在一起,并且均接GND,而数码管的驱动端a-g必须是高电平有效。

A:对 B:错 55.从理论上说,无源忆阻器一旦替代 SRAM 存储单元,能够有效降低 FPGA 中晶体管的数量和功耗,提高器件的密度,同时兼有可重构性和非易失性。

A:错 B:对 56.一般地,对相同的逻辑功能,CASE语句综合后将耗用更多的硬件资源,但是有的逻辑用CASE语句无法描述,只能用IF语句来描述。

A:对 B:错 57.在一般大规模可编程逻辑器件的数字系统设计中,只要使用IEEE库中的STD_LOGIC_1164、STD_LOGIC_ARITH、STD_LOGIC_SIGNED和STD_LOGIC_UNSIGNED四个程序包就可以了。

A:对 B:错 58.除非所有条件句中的选择值能完整覆盖CASE语句中表达式的取值,否则最末一个条件句中的选择必须用“OTHERS”表示。

A:对 B:错 59.目前我国典型的EDA实验开发系统生产厂家有杭州康芯电子,友晶科技,依元素科技等厂家。

A:对 B:错 60.动态扫描的原理是:通过一个扫描控制电路,对需要显示的结果进行逐个扫描,使七段数码管逐个进行显示。只要每个管子扫描频率超过人的眼睛视觉暂留频率,就可以达到某一时刻点亮1个七段数码管,却能享有所有七段数码管同时显示的视觉效果,而且显示也没有闪烁抖动,从而间接实现显示结果的同时显示。

A:对 B:错 61.利用结构描述方式,可采用结构化、模块化设计思想,将一个大的设计划分为许多小模块,逐一设计调试完成,然后利用结构描述方法将它们组装起来,形成更为复杂的设计。

A:对 B:错 62.计数的控制在VHDL中可用一个进程表示,而计数的控制又包含正常计数(加1操作)和边界处理(等于边界则清零)两种情况,而什么情况下进行计数或边界处理,可使用IF条件语句进行判断控制。

A:错 B:对 63.CORDIC算法的实现有两种结构方案:迭代结构和流水线结构。其中在流水线电路结构中,具有多个相同的单元电路,其中外部输入XI、YI、ZI作为第一级流水线单元的输入X(0)、Y(0)、Z(0),中间各个单元首尾相接,也就是第N个单元的输入与N-1个单元的输出X(N-1), Y(N-1), Z(N-1)相连,第N个单元的输出X(N), Y(N), Z(N)又与N+1个单元的输入相连,而最后一级处理单元的输出X(N)、Y(N)、Z(N)就是整个系统的输出XO、YO、ZO。

A:对 B:错