1.在Verilog HDL的运算符中,逻辑运算符有三种,其符号分别是“&&”、“||”和“~”。( )

A:对

B:错

答案:错

2.电子设计自动化(EDA)就是以计算机为工作平台,以EDA软件工具为开发环境,以可编程逻辑器件或者专用集成电路为目标器件设计实现电路系统的一种技术。( )

A:对

B:错

答案:对

3.在Verilog HDL中,开关级描述指具体的晶体管物理器件的描述;随着电路规模的增大,开关级描述将非常难理解。( )

A:错

B:对

答案:对

4.采取电平触发方式的always语句,经过综合之后产生的是纯组合逻辑电路,没有锁存器或触发器。( )

A:错

B:对

答案:错

5.仿真包括功能仿真和时序仿真,前者不考虑信号延时等因素,后者是在选择具体器件并完成布局布线后进行的包含延时的仿真。( )

A:错

B:对

答案:对

6.在Verilog HDL中,描述组合逻辑电路可以采用数据流描述、结构化描述和行为描述中的任意一种或多种方式;三种方式并行执行。( )

A:错

B:对

答案:对

7.在Verilog HDL中,位运算符的运算优先级高于逻辑运算符。( )

A:错

B:对

答案:对

8.利用有限状态机描述时序逻辑电路时,必须把电路精准地划分为Moore类型或者Mealy类型,否者描述的有限状态机的功能将产生错误。( )

A:对

B:错

答案:错

9.系统函数$random的作用是用于产生随机数。( )

A:对

B:错

答案:对

10.在Verilog HDL中,数字的表示包括三个部分:位宽、进制和数字;其中位宽可以省略,而进制和数字不能省略。( )

A:错

B:对

答案:错

11.过程赋值语句包括阻塞性过程赋值和非阻塞性过程赋值,前者在语句块结束时同时完成赋值,而后者在完成赋值之后才能进行下一行操作。( )

A:对

B:错

A:错 B:对 13.在编码器模块中,普通的编码器任何时刻只允许一个输入端信号输入有效,优先编码器允许两个及以上的输入端信号输入有效。( )

A:对 B:错 14.Verilog HDL的结构总是位于module和endmodule声明语句之间。( )

A:错 B:对 15.在可编程逻辑器件的基本结构中,输出缓冲电路的作用主要是对将要输出的信号进行处理,一般包括三态门、寄存器等单元。( )

A:错 B:对 16.在进行关系比较时,“4’b1101<4’bxxxx”的比较结果为假。( )

A:对 B:错 17.未来集成电路技术发展的趋势,是将整个系统集成到一个芯片上,这种芯片被称为超大规模集成电路。( )

A:错 B:对 18.在Verilog HDL中,运算符“&&”和“&”的作用没有区别。( )

A:对 B:错 19.在Verilog HDL中提供了标准的系统任务用于常用的操作,比如显示、文件输入和输出等,这些系统任务前都有标志符“¥”加以确认。( )

A:对 B:错 20.Verilog HDL提供了两种条件语句的结构,包括if-else语句和switch多路分支语句。( )

A:对 B:错 21.某同学为了完成四个8位数据a0、a1、a2和a3的加法,采用了如下三种方法实现:① assign sum=a0+a1+a2+a3;② assign sum=(a0+a1)+(a2+a3);③ assign sum=a0+(a1+a2)+a3;这两种描述方法中,性能更好的是( )

A:一样好 B:第三种方法 C:第二种方法 D:第一种方法 22.若P、R、Q都是位宽为4的输入变量,下面表达形式正确的是( )

A:input [3:0]P,[3:0]Q,[3:0]R; B:input P,Q,R[3:0]; C:input [3:0]P,Q,R; D:input P[3:0],Q,R; 23.在Verilog HDL中,有如下变量声明语句:reg [0:3] always;下列说法错误的是( )

A:变量类型为寄存器类型,只能使用在时序逻辑电路的赋值中 B:位宽不同的变量应该在不同的语句行中声明 C:不能使用always关键字定义变量名 D:位宽定义的顺序[0:3]是错的,应该定义为[3:0] 24.在一下表达式中,正确的是( )

A:&4’b1101 = 1’b1 B:~4’b1100 = 1’b1 C:4’b1010 & 4’b1101 = 1’b1 D:!4’b1010 || !4’b0000 = 1’b1 25.下面对原理图输入设计方法进行数字电路系统设计,说法不正确的是( )

A:原理图输入设计方法也可进行层次化设计 B:原理图输入设计方法一般也采用自底向上的设计实现 C:原理图输入设计方法无法对电路进行功能描述 D:原理图输入设计方法直观便捷,但不适合完成较大规模的电路系统设计 26.关于查找表(Look-up table,LUT)的原理和结构,下列说法正确的是( )

A:一般的,基于查找表结构的可编程逻辑器件属于非易失性器件 B:基于查找表的电路只能实现组合逻辑电路的功能 C:当前的CPLD大多数采用查找表结构 D:查找表本质上是一类存储器 27.某Verilog HDL的程序部分如下:always @(posedge clk) if(!rst) q<=0; else q<=q+1;若上电时rst为1,经过20个时间单位rst变为0,再经过20个时间单位rst恢复为1,则变量q被初始化为0的时刻是( )

A:上电时(0时刻) B:无法确定 C:第20个时间单位 D:第40个时间单位 28.在Verilog HDL的相关运算中,若变量A=8’b1101_0011,B=8’b1_0000_0000,则表达式“A && B”的结果是( )

A:1’b1 B:8’b1000_0000 C:8’b0000_0000 D:1’b0 29.某Verilog HDL的定时器程序部分如下::reg [9:0] count;always @(posedge clk or negedge rst) if(!rst) count<=0; else if(count==999) count<=0; else count<=count+1;assign timeup=(count==999);若系统时钟频率为50MHz,则timeup变为高电平的时间间隔是( )

A:19980ns B:20ms C:20ns D:20us 30.关于Verilog HDL中的运算符优先级别,下列说法正确的是( )

A:逻辑与“&&”和逻辑非“!”运算符属于同一优先级 B:说法都是错误的 C:项逻辑与“&&”运算符的优先级别最低 D:逻辑非“!”运算符的级别最高 31.某Verilog HDL的程序部分如下: wire [3:0] addr; assign addr=-3;则变量addr被赋值后的值为( )

A:4’b1101 B:4’bxx11 C:4’b0011 D:4’bzz11 32.资源共享设计是一种电路优化设计方法,下列对资源共享描述正确的是( )

A:资源共享是一种面积优化方法,可能会有速度优化效果 B:资源共享是一种面积优化方法,一定不会有速度优化效果 C:资源共享是一种速度优化方法,一定不会有面积优化效果 D:资源共享是一种速度优化方法,可能会有面积优化效果 33.利用Verilog HDL设计了一个八位的计数器模块,然后将计数器的输出连接到一个八位的DAC;假设该DAC的模拟参考量为电压10V,则当计数器输出为8’b10010100时,DAC的输出电压为( )

A:1.48V B:563V C:5.78V D:5.00V 34.在某Verilog HDL模块中定义了如下函数:function [2:0] my_function; input [3:0] a,b; begin if(a>b) my_function=2’b01; else if(a<b) my_function=2’b10; else my_function=2’b00; endendfunction若模块中对函数进行了调用,令c=my_function(4’b1010,4’b1100),则变量c的值为( )

A:2’b11 B:2’b01 C:2’b10 D:2’b00 35.若A=4’b0000,B=4’b0101,C=4’b0011,D=4’b0000,则下列运算结果为0的是( )

A:A||C B:B||C C:A||D D:A||B 36.请指出Altera CycloneⅣ系列中的EP4CE6F17C8这个器件属于( )

A:ARM B:FPGA C:CPU D:CPLD 37.在Verilog HDL中,声明某个变量,下列变量的取名合法的是( )

A:MY count B:00count C:&count D:_MY_count 38.某Verilog HDL的程序部分如下:reg [3:0] temp;always @(posedge clk or negedge rst) if(!rst) temp=31;则经过复位信号的初始化之后,temp的值为( )

A:31 B:5’b11111 C:4’d31 D:4’b1111 39.某测试平台的程序部分如下: reg clk; always begin #5 clk=0; #10 clk=~clk; end则变量clk的波形说法正确的是( )

A:clk一直为高电平1 B:clk的周期为20个时间单位 C:clk的周期为15个时间单位 D:clk一直为低电平0 40.某Verilog HDL的程序部分如下:reg [2:0] i;reg [4:0] num;always @(posedge clk) begin num=0; for(i=0;i<8;i=i+1) num=num+2; end若时钟上升沿到来, num的值为( )

A:0 B:16 C:形成了死循环 D:14 41.在Verilog HDL中,若定义变量i为8位寄存器类型的变量,则语句“for(i=0;i<=8;i=i+1)”执行的循环次数将为( )

A:9 B:无穷 C:8 D:7 42.某Verilog HDL的移位寄存器程序部分如下:reg [7:0] myshift;always @(posedge clk) if(!rst) myshift<=8’b00000001; ________________________为了能够实现从00000001→00000011→00000111→…→11111111的移位过程,在横线处应该添加的语句是( )

A:else myshift<={myshift[7:0],myshift[8]}; B:else myshift<=myshift<<1; C:myshift<={myshift[7:0],1’b1} D:myshift<={myshift[7:0],1} 43.关于Verilog HDL中的宏定义指令`define语句,下列说法正确的是( )

A:宏定义语句`define的作用范围仅限于当前模块 B:宏定义语句用于将一个简单的标志符代替一个复杂的字符串或表达式 C:宏定义语句`define的功能与参数类型的数据完全一模一样 D:在宏定义语句`define的行末需要加上分号 44.某Verilog HDL的程序如下(程序中间省略号略去了变量类型的声明): module exam1(a,b,c,d); input a,b; output c,d; …… always @(a or b) c=a^b; assign d=b endmodule上述程序中四个变量a、b、c和d中属于线网类型变量的是( )

A:b B:a C:c D:d 45.某Verilog HDL的模块如下: module parameter(a,b,c) input a,b; reg c; always @(*) c=a^b; endmodule关于上面模块中针对语法错误的修改,说法正确的是( )

A:always语句后面的敏感变量列表不能用“*”号,须改为“a or b” B:模块的名称选取了关键字parameter,需要修改 C:模块中没有声明输出端口 D:变量c需要声明为线网类型 46.在Verilog HDL中,关于任务和函数,下列说法正确的是( )

A:在函数中可以调用任务 B:函数有且仅有一个输入变量,输出变量由函数名本身担任 C:任务的定义和调用可以分别位于不同的模块之中 D:任务调用时,端口变量必须和任务定义时一一对应 47.目前国际上较大的可编程逻辑器件制造公司包括( )

A:华为 B:Xilinx C:小米 D:Altera 48.下面的Verilog HDL的语句,属于可综合语句的是( )

A:for循环语句 B:串行块begin-end C:while循环语句 D:并行块fork-join 49.

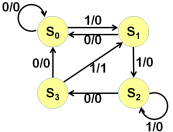

如图所示的状态转换图的功能是( )

A:用于检测“1110”的序列检测器 B:用于检测“1101”的序列检测器 C:用于检测“1100”的序列检测器 D:四进制计数器 50.假设已有全加器模块FullAdder,若在某顶层模块中调用此全加器,连线如下电路图符号所示:

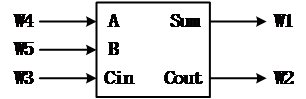

则正确的调用格式是( )

A:FullAdder U1(W1,W2,W3,W4,W5); B:FullAdder U1(A(W4),Cin(W3),B(W5),Cout(W2),Sum(W1)); C:FullAdder U1(.A(W4),.Cin(W3),.B(W5),.Cout(W2),.Sum(W1)); D:FullAdder U1(.A(W1),.B(W2),.Cin(W3),.Sum(W4),.Cout(W5));