提示:内容已经过期谨慎付费,点击上方查看最新答案

数字逻辑

- 0 输出有效的3线─8线译码器74LS138,若使输出Y3=0, 则输入量A2A1A0应为( )

- 逻辑函数中的逻辑“与”和它对应的逻辑代数运算关系为()

(36)10转换为二进制数是( )

- 用三线-八线译码器74LS138和辅助门电路实现逻辑函数Y=A2+A2´A1´,应( )。

- 下列中规模组合逻辑器件中,能够将并行数据转换成串行数据

的是( ) 与二进制数101.011等值的十进制数是()

3线—8线译码器74HC138,当片选信号S1S2´S3´为( )时,芯片被选通

对于普通编码器和优先编码器下面的说法正确的是( )

- 一个有双输入端 A、B 的或非门,当 B 分别为0、1时,输出 Y

分别为 - 以下电路中,加以适当辅助门电路,()适于实现单输出组合逻辑电路

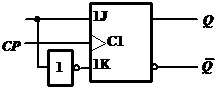

图中,由JK触发器构成了( )。

- JK触发器要实现Q*=1时,J、K端的取值为( )

- 译码器的逻辑功能是将( )

在逻辑代数基本运算法则中:A+A=( )。

- (8C)H的等值十进制数是( )

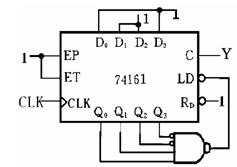

下图电路中,74LS161构成了( ) 进制计数器。

- 与十进制数209等值的二进制数为()

- 通过级联方法,把两片4位二进制计数器74LS161连接成为8位二进制计数器后,其最大模值是( )。

当变量 A、B、C 取值为101 时,下列三变量函数最小项中等于

1 的是存储8位二进制信息要( )个触发器。

当JK触发器处于翻转功能时,其输出的次态为( )。

用公式法化简逻辑函数Y=AB(A+B'C)最简与或式为( )

- 已知Y=A+AB´+A´B,下列结果中正确的是()

- 与十进制数9等值的二进制数为()

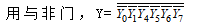

- 用公式法化简函数为最简与或式F=AB'+A'CD+B+C'+D'

- 用四选一数据选择器实现函数Y= A1A0+ A1´A0,应使 ( )

- 用公式法化简逻辑函数Y=AB'+B+A'B为最简与或式为( )

- 逻辑函数Y(A,B,C)=∑m(6,7),约束条件:m0+m4+m5=0的最简与或式为( )

对于JK触发器,输入J=0,K=1,CLK脉冲作用后,触发器的次态应为( )。

- 一位数据比较器,若A、B为两个一位数码的表示变量,当A>B时输出Y=1,则输出Y的表达式为 Y=( )

函数 Y=B'+A 中,包含的最小项个数为 ( ).

- 与二进制数1111等值的十进制数是()

- 表示一个最大的3位十进制数,所需二进制数的位数至少是( )

- 下列逻辑函数中,F恒为0的是()

下图电路中,74LS161构成了( )进制计数器。

- 逻辑函数Y(A,B,C)=∑m(0,1,2,4,6)为最简与或式为( )

如需要判断两个二进制数的大小或相等,可以使用( )电路。

- 一个8选1的数据选择器,当选择控制端A2A1A0的值分别为101时,输出端输出( )的值。

- 若J=K′,则完成( )触发器的逻辑功能.

有一个或非门构成的SR锁存器,当输入为R=0,S=1时,则Q*为()

对触发器正确的叙述是( )。

将与非门当做反相器使用时各输入端连接的方法是( )。

- 属于组合逻辑电路的部件是( )

对一个3线-8线译码器正确的叙述是( )。

按逻辑功能来划分,触发器可以分为( )。

把一个5进制计数器与一个10进制计数器串联可得到15进制计数器。

将8个“1”异或起来得到的结果为1。

数字电路中用“1”和“0”分别表示两种状态,二者通常无大小之分

计数器的模是指构成计数器的触发器的个数。

D触发器的特征方程Q*=D,而与Qn无关,所以,D触发器不是时序电路。

A:011 B:100 C:110 D:000

答案:011

A:逻辑或 B:逻辑非 C:逻辑加 D:逻辑乘

答案:逻辑乘

A:100110 B:110011 C:100100 D:101111

答案:1010BAI参考:正确选项是【C:100100】。题目中给出的数字是10,转换为二进制数需要将其除以2并取余数,直到商为0为止。由于初始数字是偶数,所以需要从低位到高位逐位除以2,并在每个位上保留商值(用0或1表示)。最后得到的结果为100100。所以,选项C是正确的。'

A:用与门,Y=Y2´Y3´ B:用与非门,Y=(Y0´Y1´Y4´Y5´Y6´Y7´)´ C:用或门,Y=Y2´+Y3´ D:用或门,Y=Y=Y0´+Y1´+Y4´+Y5´+Y6´+Y7´

答案:

A:译码器 B:数据比较器 C:数据选择器 D:加法器

答案:数据选择器

A:5.675 B:5.375 C:3.625 D:5.175

A:010 B:101 C:001 D:100

A:普通编码器和优先编码器都允许输入多个编码信号 B:普通编码器允许输入多个编码信号,优先编码器只允许输入一个编码信号 C:普通编码器只允许输入一个编码信号,优先编码器允许输入多个编码信号 D:普通编码器和优先编码器都只允许输入一个编码信号

A:七段显示译码器 B:数值比较器 C:二进制译码器 D:数据选择器

AI参考:正确选项是【D】JK触发器。JK触发器是一种具有记忆功能的逻辑电路,它有两个输入端JK,一个输出端Q,还有一个辅助输出端C。在输入信号作用下,JK触发器可以根据输入信号的变化来改变输出信号Q的状态。在给定的条件下,JK触发器可以完成特定的逻辑功能。图中所示的电路中,JK触发器是主要元件,因此答案为D。'

A:J=0,K=1 B:J=0,K=0 C:J=1,K=0 D:J=1,K=1

AI参考:正确选项是【B:J=0,K=0】。JK触发器是一种具有置位、复位、保持和记忆功能的触发器,其中Q*=1时,JK触发器的J端和K端应取值为0和0。这是因为JK触发器在时钟脉冲上升沿时,当J和K端的输入信号都为低电平(0)时,输出信号Q将保持不变;而在时钟脉冲下降沿时,当J和K端的输入信号都为低电平(0)时,输出信号Q将发生翻转,变为高电平(1)。因此,在选择JK触发器的J、K端取值时,需要考虑触发器的具体功能和应用场景。对于一般的计数器或数据存储系统,通常采用J=0、K=0或J=1、K=1的方式来实现计数或存储功能。但是,在实现Q*=1时,需要选择J=0、K=0的方式。'

A:输入的二进制代码译成对应输出的高、低电平 B:输入的二进制代码译成对应输出的二进制代码 C:输入的高、低电平译成对应输出的高、低电平 D:输入的高、低电平译成对应输出的二进制代码

A:0 B:A C:2A D:1

A:140 B:214 C:1000 D:1100

A:3 B:13 C:8 D:14

A:11010001 B:11000111 C:10011101 D:10110001

A:128 B:64 C:32 D:256

A:m1 B:m5 C:m3 D:m7

A:4 B:2 C:3 D:8

A:1 B:0 C:与原态相反 D:与原态相同

A:Y=B B:Y=A C:Y=A+B D:Y=A´+B´

A:1001 B:1010 C:0101 D:10001

A:A+CD B:A+B C:A D:1

A:D0=D2=0,D1=D3=1 B:D0=D1=1,D2=D3=0 C:D0=D2=1,D1=D3=0 D:D0=D1=0,D2=D3=1

A:B B:A+B C:A D:AB

A:AB B:B C:A D:A+B’C’

A:3 B:1 C:2 D:4

A:14 B:15 C:16 D:7

A:9 B:6 C:11 D:10

AI参考:正确答案是【D】10。一个最大的3位十进制数(最大为999)转换成二进制数为10011011,所需二进制位数为9位。但是为了表示最大的3位十进制数,还需要一个高位,所以答案为D选项的10位。'

AI参考:选项A是一个基本的逻辑函数,叫做逻辑非函数。它对输入逻辑变量进行取反操作,也就是说,如果输入变量为真(或非零),那么逻辑函数的结果为假(或零)。对于输入变量F=A⊕B,当A和B不同时为真时,函数F的结果为假,即F恒为0。所以,正确答案是选项A:F=A⊕B。'

A:16 B:9 C:10 D:12

A:数据比较器 B:译码器 C:数据选择器 D:编码器

A:D0 B:D5 C:D3 D:D1

A:保持 B:不定 C:0 D:1

A:它的Q端反映了它的状态 B:它是最简单的时序逻辑电路 C:不同类型的触发器可以相互转换 D:它是组合逻辑电路的基本组成单元

A:选一个输入端作为输入,其余的输入端接高电平 B:选一个输入端作为输入,其余的输入端接低电平 C:选一个输入端作为输入,其余的输入端悬空 D:各输入端并接作为输入

A:比较器 B:编码器 C:译码器 D:计数器

A:它有3个主要输入端 B:它是二进制译码器 C:它有8个主要输入端 D:同一时间只有一个输出端是有效的

A:JK 触发器 B:T 触发器 C:RS触发器 D:D触发器

A:对 B:错

A:对 B:错

A:错 B:对

A:对 B:错

A:错 B:对

温馨提示支付 ¥2.15 元后可查看付费内容,请先翻页预览!