第四章单元测试

对于维持阻塞结构的D触发器,当CP=1期间,输入信号D由1跳转到0,则由于

=D,输出状态Q也由1跳转到0。

移位寄存器除了可以寄存代码,还可实现数据的串行-并行转换,但不能用于数值运算和处理。

若要设计一个能产生序列信号001111011的移位寄存器序列信号发生器,则至少需要4个触发器。

所有触发器的时钟端并没有完全连接在一起的时序逻辑电路是异步时序逻辑电路。

在设计稳定性和工作频率要求较高的中大规模时序系统时一般采用同步时序电路来设计。

4位移位寄存器,现态Q0Q1Q2Q3为1100,经左移1位后其次态为 。

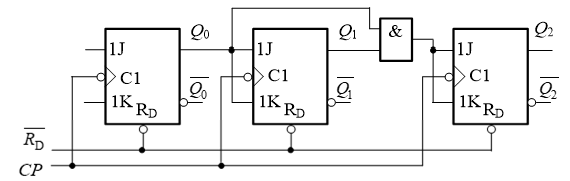

电路如图所示。设电路中各触发器当前状态Q2 Q1 Q0为110,请问时钟CP作用下,触发器下一状态为 。

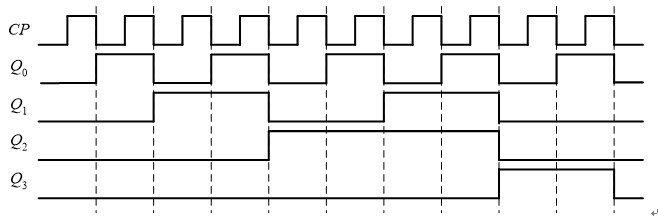

如图所示为某计数器的时序图,由此可判定该计数器为 。

假设JK触发器的现态Qn=0,要求Qn+1=0,则应使 。

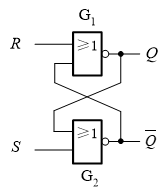

如图所示为由或非门构成的基本SR锁存器,输入S、R的约束条件是 。

A:对 B:错

答案:错

A:对 B:错

A:对 B:错

A:对 B:错

A:对 B:错

A:

0011或1111

B:1011或1110

C:0011或1011

D:1000或1001

A:101

B:111 C:110 D:010

A:

八进制计数器

B:九进制计数器

C:四进制计数器

D:十进制计数器

A:

J=K=1

B:J=0,K=×

C:J=1,K=×

D:J=×,K=0

A:S+R=1 B:S+R=0 C:SR=1 D:SR=0

温馨提示支付 ¥3.00 元后可查看付费内容,请先翻页预览!