武汉科技大学

- 描述时序逻辑电路的方程组包括( )

- 单稳态触发器常用于( )

- 激励方程组描述了触发器的激励信号与( )的关系。

- 以下不属于四输入变量组成的最大项的是( )。

- 与异步计数器相比,同步计数器( )。

- 8线-3线优先编码器的输出状态为100,则它的输入状态

可以是( )。

可以是( )。 - 下列信号中,( )与输入信号相关。

- 双稳态触发器的常见电路结构有( )。

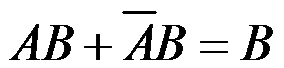

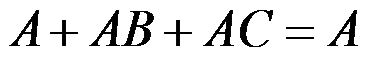

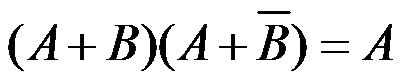

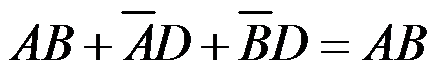

- 下列关于逻辑函数化简正确的是( )。

- 十进制数转换为二进制数的转换规则为( )。

- 噪声容限表示门电路的抗干扰能力。电路的噪声容限愈大,其抗干扰能力愈强。( )

- 驱动共阳极七段显示器的显示译码器,其输出为高电平有效。( )

- 用555定时器构成的施密特触发器可以改变电路输出波形的频率。( )

- 使用格雷码的方案对时序电路输出状态进行编码可以减少发生竞争-冒险的可能。( )

- A/D转换器的位数越多,各离散电平之间的差值越小,量化误差越小。( )

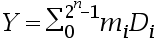

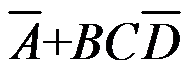

- 数据选择器的输出方程一定可以表示为

的形式。( )

的形式。( ) - 二进制代码中8421BCD码、5421BCD码格雷码等都是有权码,而余3码、余3循环码等都是无权码。( )

- 施密特触发器具有两个稳态,而单稳态触发器电路只有一个稳态。( )

- 74x139中有两个一样的2线-4线译码器,它们共用接地和接电源端口。( )

- A/D转换器的二进制数的位数越多,量化单位Δ越小。( )

- 逻辑函数表达式中的真值表,逻辑表达式,逻辑电路图,波形图等之间是可以相互转换的。( )

- 按照国家标准,数据从低位向高位移动称之为右移。( )

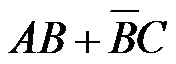

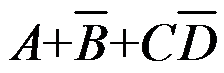

- 当变量A,B,C取值分别为101时,计算函数

的值为0。( )

的值为0。( ) - 4位数值比较器在比较两个4位二进制数的大小时,先比较的是最高位的大小。( )

- 已知逻辑函数A + B = A+ C,则B = C。( )

- 一个8位D/A转换器的最小输出电压增量为0.02V,当输入代码为01001100时,输出电压Vo为多少伏?( )

- 将随时间连续变化的模拟量转换为在时间上离散的模拟量的过程称为( )。

- 对于JK触发器,若

,则实现的是( )触发器的功能。

,则实现的是( )触发器的功能。 - 两个4位二进制数相加,最高位相加相当于( )相加。

- 将两个模为10的计数器串联连接以后可以形成一个模为( )的计数器。

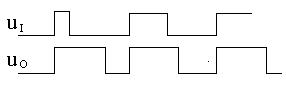

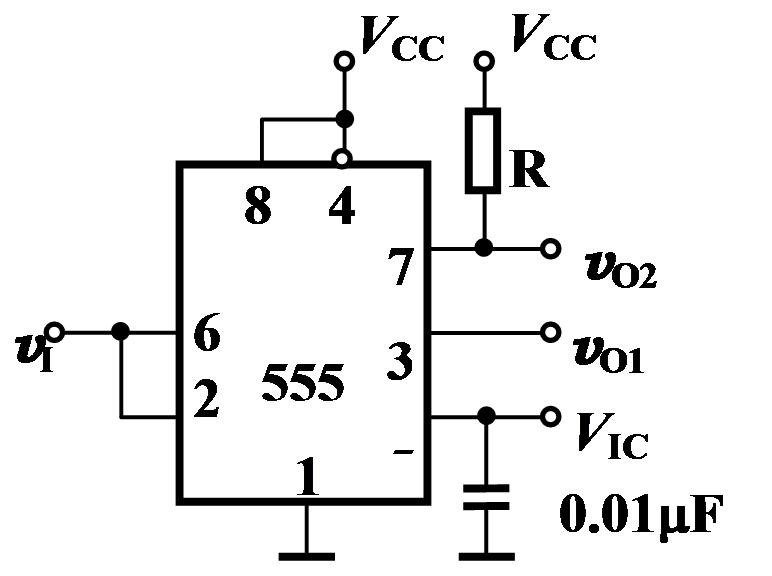

- 某电路的输入波形 uI 和输出波形 uo 如下图所示,则该电路为( )。

- 把一个4进制计数器和一个5进制计数器串联,可以构成一个( )进制计数器。

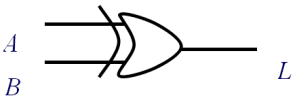

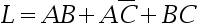

7、 逻辑门如图所示 ,则输入A,B与输出L之间的逻辑关系是( )。- 只用3线-8线译码器74x138构成6线-64线译码器,需要( )片74x138。

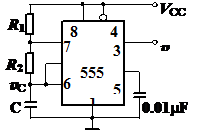

- 图3所示电路为由555定时器构成的( )。

[

[ - 将二进制数(1001.01101)B转换为十进制数是( )。

- 半加器的和输出信号S与两个加数的A、B之间是( )逻辑关系。

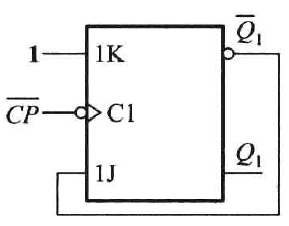

- 下图所示的电路和( )触发器的功能是一样的。

- 以下电路中,不是时序逻辑电路的是( )。

- 以下哪个器件有两个稳态且有两个不同的触发电平,具有回差特性?( )

- 多谐振荡器可产生的波形是( )

- 能起定时作用的电路是( )

- 欲将8421BCD码转换为余三码,只需要一片( )。

- N沟道场效应管的漏极电流由( )的漂移运动形成。

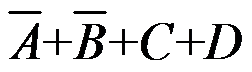

- 使逻辑函数

为1的最小项有( )个。

为1的最小项有( )个。 - 仿照74HC85设计一个8位的数值比较器,需要的输入和输出端口的数量是( )。

- PN结正偏是指( )。

- 用4选1的数据选择器实现逻辑函数

时,若将

时,若将 、

、 接入选择输入端

接入选择输入端 ,则标记为10的数据输入端

,则标记为10的数据输入端 应该输入的数据是( )。

应该输入的数据是( )。 - 用555定时器构成单稳态触发器,其输出的脉宽为( )

- 单稳态触发器的输出脉冲宽度取决于( )

A:状态方程组

B:激励方程组

C:输出方程组

D:输入方程组

答案:输出方程组###状态方程组###激励方程组

A:延时

B:整形 C:计数 D:定时

答案:延时###定时

A:触发器的次态

B:输入信号

C:触发器的现态

D:输出信号

答案:输入信号###触发器的现态

A:

B:

C:

D:

答案:

A:受到统一时钟脉冲信号的控制

B:结构更复杂

C:触发器利用率更高

D:工作速度更快

答案:受到统一时钟脉冲信号的控制###结构更复杂###工作速度更快

A:00111000

B:00011111

C:00011100

D:00011110

答案:00011100###00011111###00011110

A:触发器的次态

B:触发器的激励

C:穆尔型输出

D:米利型输出

答案:米利型输出###触发器的激励###触发器的次态

A:主从触发器

B:利用传输延迟的触发器

C:逻辑门控触发器

D:维持阻塞触发器

答案:主从触发器###维持阻塞触发器###利用传输延迟的触发器

A:

B:

C:

D:

答案:

A:整数部分转换采用除2取余,先得到的余数作为二进制数的高位,后得到的余数作为二进制数的低位。

B:整数部分转换采用除2取余,先得到的余数作为二进制数的低位,后得到的余数作为二进制数的高位。

C:小数部分转换采用乘2取整,先得到的余数作为二进制数的高位,后得到的余数作为二进制数的低位。

D:整数部分和小数部分需要分开进行

A:错 B:对

A:错 B:对

A:错 B:对

A:错 B:对

A:对 B:错

A:对 B:错

A:错 B:对

A:错 B:对

A:错 B:对

A:错 B:对

A:错 B:对

A:对 B:错

A:错 B:对

A:对 B:错

A:对 B:错

A:1.52V

B:0.76V C:3.04V D:1.40V

A:采样 B:量化

C:编码 D:保持

A:T’

B:SR

C:D

D:T

A:计数器

B:一位全加器

C:一位半加器

D:加法器

A:64

B:100

C:20

D:10

A:JK触发器

B:单稳态触发器 C:反相器 D:施密特触发器

A:5

B:9

C:20

D:4

A:或

B:与

C:同或

D:异或

A:8

B:7

C:6

D:9

A:施密特触发器 B:单稳态触发器 C:多谐振荡器

D:T触发器

A:9.40625

B:5.40625

C:9.20625

D:9.68

A:异或

B:或

C:与

D:与非

A:T’

B:T

C:D

D:SR

A:译码器

B:触发器

C:计数器

D:寄存器

A:施密特触发器 B:555定时器

C:多谐振荡器 D:单稳态触发器

A:矩形脉冲 B:三角波 C:锯齿波

D:正弦波

A:多谐振荡器 B:施密特触发器 C:编码器

D:单稳态触发器

A:译码器

B:加法器

C:编码器

D:数据选择器

A:自由电子和空穴

B:正离子

C:自由电子

D:空穴

A:6

B:4

C:8

D:7

A:16, 2

B:16, 3

C:8, 2

D:8, 3

A:N区电位高于P区

B:与外加电压无关

C:P区电位高于N区

D:P区和N区电位相等

A:0

B:

C:

D:1

A:1.1RC B:1.4RC C:1.8RC

D:0.7RC

A:触发脉冲的幅度

B:电路本身的电阻、电容参数 C:触发脉冲的宽度 D:电源电压的数值

温馨提示支付 ¥5.00 元后可查看付费内容,请先翻页预览!