泰山学院

- 下面的库中不需要显式打开的是( )。

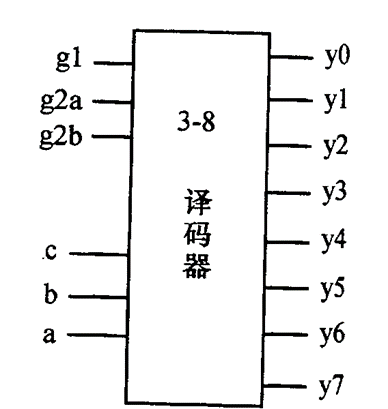

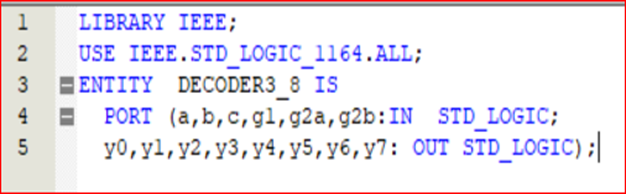

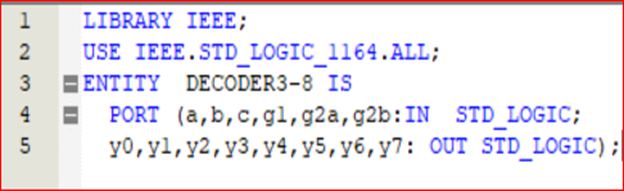

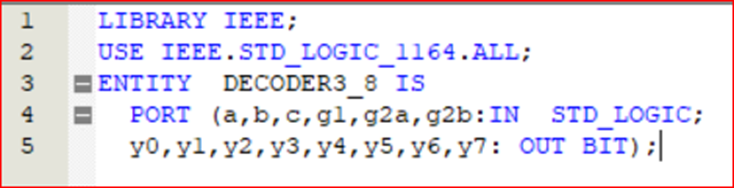

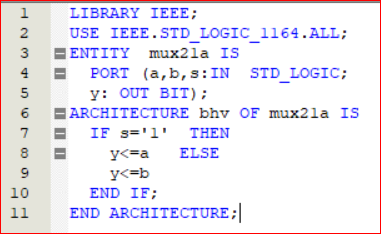

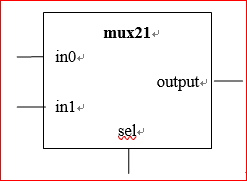

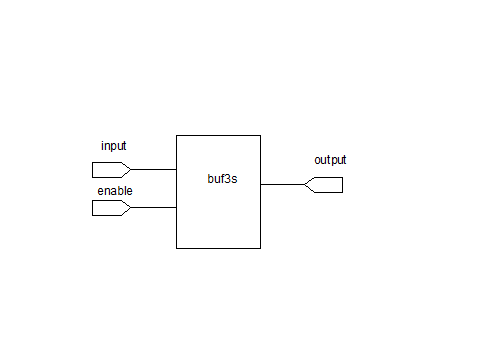

- 针对给出的电路图中的模块进行实体描述,各选项中

不正确的是( )。

不正确的是( )。 - 关于元件封装(打包)的描述正确的是( )。

- 下面关于状态机的说法正确的是( )。

- 在所有关于CASE语句和WITH_SELECT语句的描述中找出正确的选项:( )。

- 后缀是.BDF表明该文件类型是VHDL设计文件。( )

- 从可靠性来讲,一般单进程FSM高于多进程FSM。( )

- VHDL的仿真文件的后缀是.VWF。( )

- 综合器是完成综合的工具软件。( )

- 大规模可编程逻辑器件的两种主流器件就是FPGA和CPLD。( )

- INTEGER数据类型最能够代表实际数字电路信号特征。( )

- EDA设计的基本单位是项目Project,所以设计前必须先创建Project。( )

- FPGA和PLD器件是大规模可编程逻辑器件的两种主流器件。( )

- 'B'和"B"是相同的。( )

- EDA仿真分为功能仿真和时序仿真两种。( )

- 综合器就是完成VHDL综合使用的PLD器件。( )

- EDA的数据对象必须先定义才能使用。( )

- 体现实际数字电路信号特征最典型的数据类型是 BIT型。 ( )

- 使用符号化定义的枚举类型,枚举类型文字元素的编码通常是自动设置的。( )

- 并行语句可以同时执行。( )

- 仿真延时分为固有延时和惯性延时两种。( )

- 安全状态机并非不会出现非法状态,而是能够通过合理设计,在非法状态出现时能够回到合法状态。( )

- 信号零延时并不是延时时间为零,而是指延时时间为默认的δ延时。( )

- Quartus II的综合器是混合综合器,可以完成全程综合。( )

- 有限状态机主要用来设计数字系统中的控制模块。( )

- 打开要使用的程序包的关键词是 ( )。

- 下列哪个流程是基于EDA软件的正确的FPGA / CPLD设计流程:( )

- 的给出的赋值符选项中,常量使用 ( )。

- 在横线处应选择:( )。IF clr='0' THEN qtmp:="00000000"; ELSE qtmp:=qtmp+1; _______;

- STD_LOGIC型数据有几种取值?( )。

- 下面的程序书写格式正确的是( )。

- QuartusII的仿真波形文件类型为( )。

- VHDL的WORK库是用户设计的现行工具库,用于存放( )的工程项目。

- GAL是指( )。

- 下面哪一个可以用作VHDL中的合法的实体名( ) 。

- QuartusII的VHDL文本设计文件类型为( )。

- 一个设计实体(电路模块)包括实体与结构体两部分,结构体描述 ( )。

- PLA是指( )。

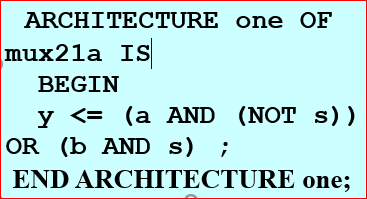

- 给出下面的VHDL描述类型的归类并填到括号:( )。

- 在QuartusII集成环境中为图形文件产生一个元件符号的主要用途是( )。

- 打开要使用的资源库的关键词是 ( )。

- https://image.zhihuishu.com/zhs/doctrans/docx2html/202008/c802e0a7c5c44f20b399901badcac017.png

- 在一个VHDL设计中data1、data2是std_logic型信号,下面表达式正确的是( )。

- 给出的多个库选项中需要显式打开的只有 ( )。

- https://image.zhihuishu.com/zhs/doctrans/docx2html/202008/e01a601a149b47a988f21f037856f9cb.png

- 子程序中的语句都是( )。

- 下列是EDA技术应用时设计的主要环节:A. 原理图/HDL文本输入; B. 适配; C. 时序仿真; D. 编程下载; E. 硬件测试; F. 综合。请选择合适的顺序构成基于EDA软件的FPGA / CPLD设计流程:( )。

- 流水线设计是一种优化方式,下列( )项对资源共享描述正确。

- 如果在进程中使用完整的IF语句,那么综合后的结果实现的是( )。

- VHDL的端口说明语句声明端口为输入方向,应该使用选项( )。

A:IEEE B:WORK C:STANDARD

答案:STANDARD###WORK

A:

B:

B: C:

C:

答案:

A:只能在高层设计中调用底层元件 B:封装后供其他设计调用该元件 C:只能在底层设计中调用顶层元件

答案:只能在高层设计中调用底层元件###封装后供其他设计调用该元件

A:N进程状态机的N是指主控进程的个数; B:状态机描述程序中有几个进程就是几进程状态机; C:有限状态机主要用来描述数字系统中的控制模块; D:只要是具有顺序递进工作特征的电路就可以用状态机来描述。

答案:N进程状态机的N是指主控进程的个数;###只要是具有顺序递进工作特征的电路就可以用状态机来描述。###有限状态机主要用来描述数字系统中的控制模块;

A:CASE语句和WITH_SELECT语句都是顺序语句; B:CASE语句是顺序语句,WITH_SELECT语句是并行语句; C:表达的条件集合必须是完备的。 D:都可以用来表达多重并列条件的选择; E:表达的条件之间必须是互斥的;

答案:表达的条件集合必须是完备的。###表达的条件之间必须是互斥的;###CASE语句和WITH_SELECT语句都是顺序语句;###都可以用来表达多重并列条件的选择;

A:错 B:对

答案:错

A:对 B:错

答案:对

A:错 B:对

答案:A:错

A:对 B:错

答案:A

A:错 B:对

A:对 B:错

A:对 B:错

A:对 B:错

A:错 B:对

A:错 B:对

A:错 B:对

A:对 B:错

A:错 B:对

A:错 B:对

A:错 B:对

A:对 B:错

A:错 B:对

A:错 B:对

A:对 B:错

A:对 B:错

A:LIBRARY B:ENTITY C:USE D:PORT

A:原理图/HDL文本输入→适配→综合→功能仿真→编程下载→硬件测试 B:原理图/HDL文本输入→功能仿真→综合→适配→编程下载→硬件测试 C:原理图/HDL文本输入→功能仿真→适配→编程下载→综合→硬件测试 D:原理图/HDL文本输入→功能仿真→综合→编程下载→→适配硬件测试;

A::= B:<= C:=

A:END IF B:END PROCESS C:BEGIN

A:2; B:1; C:9; D:3

A:

B:

B: C:

C:

A:.bdf B:.scf C:.vwf D:.vhd

A:图形文件 B:用户自己设计 C:公共程序 D:共享数据

A:通用逻辑阵列。 B:通用阵列逻辑 C:可编程逻辑阵列 D:可编程阵列逻辑

A:OUT1 B:VARIABLE C:OR D:SIGNAL

A:.bdf B:.vhd C:.vwf D:.scf

A:器件外部特性 B:器件的内部功能 C:器件的综合约束 D:器件外部特性与内部功能

A:可编程阵列逻辑 B:通用阵列逻辑 C:可编程逻辑阵列 D:通用逻辑阵列

A:行为描述 B:数据流(RTL)描述 C:结构描述

A:被高层次电路设计调用 B:仿真 C:综合 D:编译

A:PORT B:USE C:LIBRARY D:ENTITY

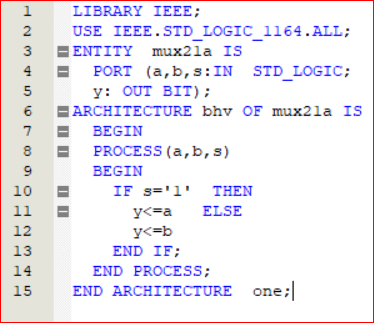

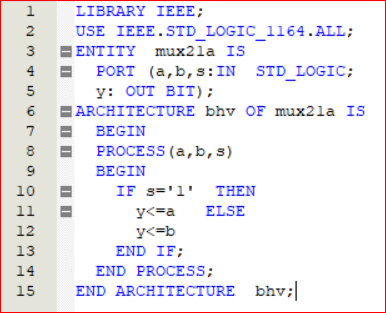

A:

B:

B:

A:data1 <= data2 +’’1’’ B:Data1 <=data1+1 C:data1 <= data2 AND ‘1’。 D:data1 <=data2 & ‘1’

A:WORK B:STANDARD C:IEEE

A:MEALY型 B:MOORE型

A:顺序语句 B:并行语句 C:既有并行语句也有顺序语句 D:既非并行语句也非顺序语句。

A:AFBCDE B:DAFBCE C:ABDFCE D:ABCDEF

A:速度优化方法,可能会有面积优化效果 B:面积优化方法,可能会有速度优化效果 C:面积优化方法,不会有速度优化效果 D:速度优化方法,不会有面积优化效果

A:组合逻辑电路 B:双向电路 C:三态控制电路 D:时序逻辑电路

A:BUFFER B:OUT C:IN D:INOUT

温馨提示支付 ¥5.00 元后可查看付费内容,请先翻页预览!