温州大学

- 采取电平触发方式的always语句,经过综合之后产生的是纯组合逻辑电路,没有锁存器或触发器。( )

- 在时序逻辑电路设计中,全局复位的方式分为同步复位和异步复位,两者的区别在于执行复位操作是否需要时钟信号的参与。( )

- 过程赋值语句包括阻塞性过程赋值和非阻塞性过程赋值,前者在语句块结束时同时完成赋值,而后者在完成赋值之后才能进行下一行操作。( )

- 在Verilog HDL中,开关级描述指具体的晶体管物理器件的描述;随着电路规模的增大,开关级描述将非常难理解。( )

- Verilog HDL提供了两种条件语句的结构,包括if-else语句和switch多路分支语句。( )

- 设计时序逻辑电路时,如果寄存器类型的变量没有初始化,将默认为低电平0。( )

- FPGA器件的规模可以做的很大,其内部主要由大量的逻辑块构成,一般情况下查找表是逻辑块的主要构成部分,因此可以实现非常复杂的逻辑功能。( )

- 从某种方面来看,模块可以分为两种类型。一种是“功能模块”,即描述某种电路系统结构和功能,以综合或者提供仿真模型为设计目的;另一种是 “测试平台”,即为功能模块的测试提供信号源激励、输出数据监测。( )

- 在Verilog HDL的运算符中,逻辑运算符有三种,其符号分别是“&&”、“||”和“~”。( )

- 在数字电路设计中,流水线设计就是将组合逻辑系统地分割,并在各个部分之间插入寄存器,并暂存中间数据的方法。流水线设计的目的是将一个大操作分解成若干的小操作,每一步小操作的时间较小,所以能提高频率。( )

- Verilog HDL的结构总是位于module和endmodule声明语句之间。( )

- 可编程逻辑器件属于半定制专用集成电路。( )

- 在可编程逻辑器件的基本结构中,输出缓冲电路的作用主要是对将要输出的信号进行处理,一般包括三态门、寄存器等单元。( )

- 仿真包括功能仿真和时序仿真,前者不考虑信号延时等因素,后者是在选择具体器件并完成布局布线后进行的包含延时的仿真。( )

- 在Verilog HDL中,描述组合逻辑电路可以采用数据流描述、结构化描述和行为描述中的任意一种或多种方式;三种方式并行执行。( )

- 建立时间(setup-up time)指的是触发器的输入数据必须在时钟有效沿到来之前的一段时间保持稳定;若建立时间不满足要求,则触发器在时钟有效沿到来时不能稳定地存储数据。( )

- 在编码器模块中,普通的编码器任何时刻只允许一个输入端信号输入有效,优先编码器允许两个及以上的输入端信号输入有效。( )

- 在关键字begin…end之间的语句是顺序执行的,而在fork…join之间的语句是并行执行的。( )

- 基于快闪存储器(Flash)的CPLD是非易失性器件,基于静态存储器(SRAM)的FPGA是易失性器件。( )

- 在Verilog HDL中,赋值语句包括连续赋值语句和过程赋值语句。( )

- 下列属于可编程逻辑器件典型应用领域的是( )

- 变量a、b、c、d、e和f的位宽均为1,且a=1’b1,b=1’b0,若c=a+b,d=a|b,e=a || b,f=a^b,则c、d、e和f四个变量中值为1’b1的有( )

- 下列语句经过综合之后将产生锁存器的是( )

- 大型数字逻辑电路设计采用的知识产权核(Intellectual Property core,IP)包括( )

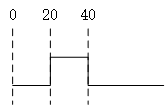

- 某测试平台为了对变量a进行初始化,以产生如下图所示的波形:

initial begin

……

end

则在上述初始化语句的省略部分可以采用的语句是( ) - 在Verilog HDL中,有如下变量声明语句:reg [0:3] always;下列说法错误的是( )

- 已知a=3’b101,b=2’b001,那么{a,2’b11,b} =( )

- 某Verilog HDL的程序部分如下:assign Ax=Bx;always @(posedge clk) Count=Cx+1;在上面程序中出现的变量需要声明为寄存器类型的是( )

- 某Verilog HDL的程序部分如下:reg [7:0] A;reg [2:0] sum,op1,op2;initial begin sum=op1+op2; A[ _____ ]=sum; end在上面的横线处填写如下内容,不会引起语法错误的是( )

- 在Quartus软件环境中,编译Verilog源程序时要求( )

- 请指出Altera CycloneⅣ系列中的EP4CE6F17C8这个器件属于( )

- 在Verilog HDL中,若定义变量i为8位寄存器类型的变量,则语句“for(i=0;i<=8;i=i+1)”执行的循环次数将为( )

- 在七段显示译码模块中,给共阴极的数码管驱动;若要让其显示数字“3”,则译码器的输出应该是( )

- 某Verilog HDL的程序部分如下:always @(A or B) begin Y1=A&~B | B&~A; Y2=A+B; Y3=^A; end下列说法正确的是( )

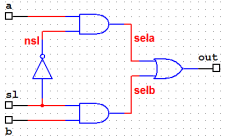

下图的电路连接表示的电路功能是( )- 在Verilog HDL的相关运算中,若变量A=8’b1101_0011,B=8’b1_0000_0000,则表达式“A && B”的结果是( )

- 下面对原理图输入设计方法进行数字电路系统设计,说法不正确的是( )

- 某Verilog HDL的程序如下:_______ exam3(A,B,C,D,E);_______ A,B,C,D;_______ E;_______ E=A&B | C|D;_______横线处可以填写①input;②output;③module;④endmodule;⑤assign。正确的填写顺序是( )

- 下列Verilog HDL的标志符合法的是( )

- 某Verilog HDL的程序部分如下: wire [3:0] addr; assign addr=-3;则变量addr被赋值后的值为( )

- 基于Quartus进行FPGA设计开发的流程,下列说法错误的是( )

- 一个较大的组合逻辑电路总延时为100ns,采用流水线将它分为两个较小的组合电路,理论上电路的最高工作频率可达( )

- 关于Verilog HDL中的宏定义指令`define语句,下列说法正确的是( )

- 某Verilog HDL的程序部分如下:reg [3:0] temp;always @(posedge clk or negedge rst) if(!rst) temp=31;则经过复位信号的初始化之后,temp的值为( )

- 若某寄存器类型的变量count能够完成50进制的计数,则必须声明count的位宽至少为( )

- 资源共享设计是一种电路优化设计方法,下列对资源共享描述正确的是( )

- 在有限状态机设计中,n位的状态寄存器至多可以表征2n个状态。若状态机中出现了多余状态(也叫无效状态),通常的处理方式是( )

- 下列哪些Verilog HDL的基本门级元件不是多输入的( )

- 若A=4’b0000,B=4’b0101,C=4’b0011,D=4’b0000,则下列运算结果为0的是( )

- 某Verilog HDL的移位寄存器程序部分如下:reg [7:0] myshift;always @(posedge clk) if(!rst) myshift<=8’b00000001; ________________________为了能够实现从00000001→00000011→00000111→…→11111111的移位过程,在横线处应该添加的语句是( )

A:对 B:错

答案:错

A:对 B:错

答案:对

A:对 B:错

答案:错

A:错 B:对

答案:对

A:错 B:对

答案:错

A:错 B:对

答案:错

A:对 B:错

答案:对

A:错 B:对

答案:对

A:错 B:对

答案:错

A:错 B:对

A:对 B:错

A:对 B:错

A:错 B:对

A:对 B:错

A:错 B:对

A:错 B:对

A:错 B:对

A:错 B:对

A:对 B:错

A:对 B:错

A:嵌入式处理

B:数字信号处理

C:接口逻辑的设计

D:可重构计算和可进化硬件

A:d B:f

C:c D:e

A:assign c=(a>b)?a:b;

B:always @(a or b)

if(a>b) c=a;

C:always @(*)

if(a>b) c=a;

else c=0;

D:always @(a or b)

if(a>b) c=a;

else if(a<b) c=b;

A:固核 B:硬核 C:软核 D:双核

A:a=0;

#20 a=1;

#40 a=0;

B:a=0;

forever #20 a=~a;

C:a<=0;

#20 a<=1;

#40 a<=0;

D:a=0;

#20 a=1;

#20 a=0;

A:变量类型为寄存器类型,只能使用在时序逻辑电路的赋值中

B:位宽不同的变量应该在不同的语句行中声明

C:不能使用always关键字定义变量名

D:位宽定义的顺序[0:3]是错的,应该定义为[3:0]

A:1011101 B:8’b10111001 C:10111001 D:7’b1011101

A:Cx

B:Ax C:Count D:Bx

A:sum:op1

B:0:sum C:sum:0 D:2:0

A:项目名称和顶层模块的名称不同

B:必须处理所有的警告信息

C:项目名称和顶层模块的名称相同

D:项目名称和顶层模块的名称可以相同也可以不同

A:CPU B:CPLD C:FPGA D:ARM

A:7 B:无穷

C:8 D:9

A:7’b1111100 B:7’b1111001

C:7’b0000110 D:7’b1111000

A:若A=1’b0,B=1’b1,则Y1=0

B:Y2=A+B属于阻塞性赋值语句,执行该语句时,先计算A+B的值,然后赋给Y2,在此过程中不能运算其他语句

C:若A=4’b1011,则Y3=0

D:都不正确

A:加法器

B:二选一的多路选择器 C:译码器 D:编码器

A:8’b0000_0000 B:1’b1 C:1’b0

D:8’b1000_0000

A:原理图输入设计方法无法对电路进行功能描述

B:原理图输入设计方法一般也采用自底向上的设计实现

C:原理图输入设计方法直观便捷,但不适合完成较大规模的电路系统设计

D:原理图输入设计方法也可进行层次化设计

A:④①②⑤③ B:③①②⑤④ C:③②①⑤④

D:①②③④⑤

A:_A10_15 B:A10#15 C:’b15

D:74LS161

A:4’bzz11

B:4’b0011 C:4’bxx11 D:4’b1101

A:在Quartus中的设计输入包括原理图输入、HDL输入、EDIF网表输入等方式

B:布局布线是将综合后的电路针对某一具体的目标器件进行逻辑映射

C:功能仿真是针对设计的电路的基本功能进行验证,不涉及时序

D:编译和综合只针对编写的程序检查语法错误

A:20MHz

B:20KHz C:10KHz D:10MHz

A:在宏定义语句`define的行末需要加上分号

B:宏定义语句`define的功能与参数类型的数据完全一模一样

C:宏定义语句`define的作用范围仅限于当前模块

D:宏定义语句用于将一个简单的标志符代替一个复杂的字符串或表达式

A:4’d31 B:31 C:5’b11111 D:4’b1111

A:7

B:6 C:5 D:4

A:资源共享是一种速度优化方法,可能会有面积优化效果

B:资源共享是一种面积优化方法,可能会有速度优化效果

C:资源共享是一种面积优化方法,一定不会有速度优化效果

D:资源共享是一种速度优化方法,一定不会有面积优化效果

A:将状态转换图画满2n个状态

B:用default分支决定一旦进入多余状态后返回初始的有效状态

C:降低状态寄存器的位宽

D:忽略该状态,不做处理

A:nand B:nor C:and D:not

A:A||B B:B||C C:A||D

D:A||C

A:else myshift<={myshift[7:0],myshift[8]};

B:myshift<={myshift[7:0],1’b1}

C:myshift<={myshift[7:0],1} D:else myshift<=myshift<<1;

温馨提示支付 ¥5.00 元后可查看付费内容,请先翻页预览!