第八章 常见组合逻辑电路的描述和验证:⑴了解并行电路和串行电路的优点和缺点; ⑵掌握常见的组合逻辑电路的描述和验证; ⑶掌握利用Verilog HDL的三种描述方式描述各种组合逻辑电路; ⑷学会组合逻辑电路描述的要点。8.1加法器:本节主要介绍一位半加器和全加器的描述,以及串行加法器、并行加法器、超前进位加法器的描述和验证。[单选题]在Verilog HDL中,直接利用乘法运算符描述的乘法器,经过综合之后生成的乘法器属于( ) 选项:[超前进位乘法器

8.2乘法器:本节主要介绍并行乘法器、移位相加乘法器的描述和验证。

, 并行乘法器

, 串行乘法器

, 移位相加乘法器

]

[单选题]在Verilog HDL中,利用加法运算符可以描述并行加法器。现在要完成一个纯组合逻辑电路的加法器,下列描述正确的是( ) 选项:[always @(posedge clk)

{cout,sum}=a+b;

, always @(a or b)

{cout,sum}=a+b;

, always @(a or b)

{sum,cout}=a+b;

, always @(posedge clk)

{sum,cout}=a+b;

]

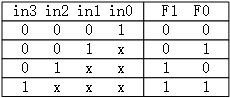

[单选题]在Verilog HDL中,为了完成具有优先功能的四-二编码器(功能表如图所示),

部分程序如下:

always @(in3,in2,in1,in0)

________

4’b0001:{F1,F0}=2’b00;

4’b001x:{F1,F0}=2’b01;

4’b01xx:{F1,F0}=2’b10;

4’b1xxx:{F1,F0}=2’b11;

default:{F1,F0}=2’bxx;

endcase

空格处应填( ) 选项:[casex(in3,in2,in1,in0)

, casex({in3,in2,in1,in0})

, case({in3,in2,in1,in0})

, case(in3,in2,in1,in0)

]

[单选题]某Verilog HDL的程序如下:

module top(A,B,Con,out);

input A,B,Con;

output out;

assign out=(Con)?A:B;

endmodule

该程序描述的模块功能是( ) 选项:[一位数值比较器

, 二选一的多路选择器

, 四选一的多路选择器

, 半加器

]

[单选题]在Verilog HDL中描述组合逻辑电路,下列说法错误的是( ) 选项:[行为描述只能用来描述时序逻辑电路

, 如果知道电路输出的表达式,可以采用数据流描述

, 数据流描述只能用来描述组合逻辑电路

, 如果知道电路原理图,可以采用结构化描述

]

温馨提示支付 ¥1.00 元后可查看付费内容,请先翻页预览!