山东科技大学

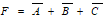

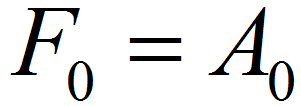

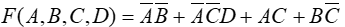

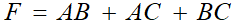

- 函数

和

和 不相等( )。

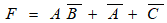

不相等( )。 - 函数

和函数

和函数 不相等( )

不相等( ) - 此逻辑函数Y1=Σm(2,6,8,9,11,12,14)可能存在着竞争-冒险。( )

- 在CMOS电路中,输入端允许悬空。( )

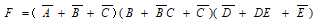

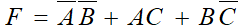

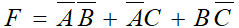

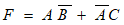

- 函数

的对偶式为

的对偶式为 。( )

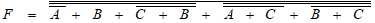

。( ) - 试用74LS138译码器和与非门实现一位全加器,设输入变量为Ai,Bi,Ci-1,Ci-1表示低位往当前位的进位,Si表示和,Ci表示当前位往高位的进位,则按照如下电路设计,可以实现该一位全加器的功能。

( )

( ) - https://image.zhihuishu.com/zhs/doctrans/docx2html/202103/0ab6a4fd555a4c4da8525e3041a0f3c8.png

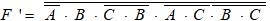

如下图所示的逻辑电路,可以实现F=AB的功能。

( )

( )- 74LS160和74LS161都是模为16的加1计数器。( )

- https://image.zhihuishu.com/zhs/doctrans/docx2html/202103/d1aa70b60aed478dbc5668d4623827c1.jpeg

- https://image.zhihuishu.com/zhs/doctrans/docx2html/202103/c754b6ef4dd54fa2a368efe0b780f366.jpeg

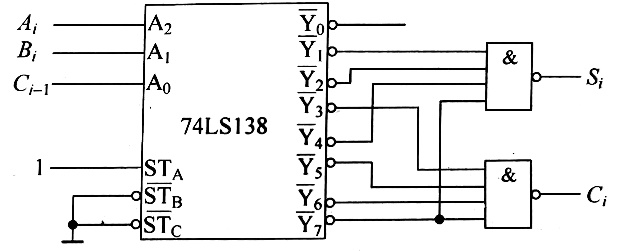

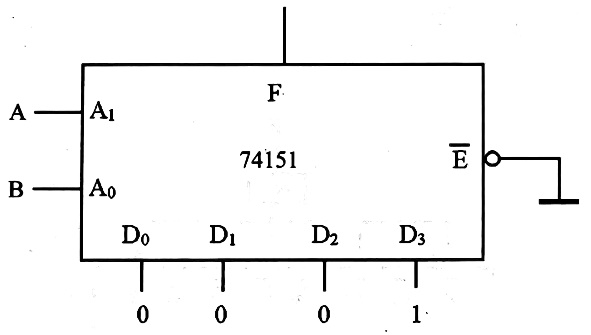

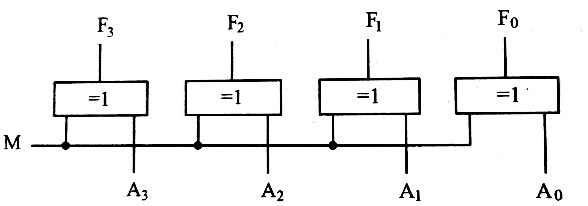

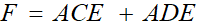

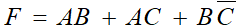

- 试分析如下电路,分析M=0时输出逻辑函数的表达式为

,

, ,

, ,

,

( )

( ) - FPGA与CPLD的主要差别在于集成度( )

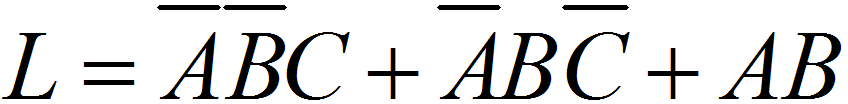

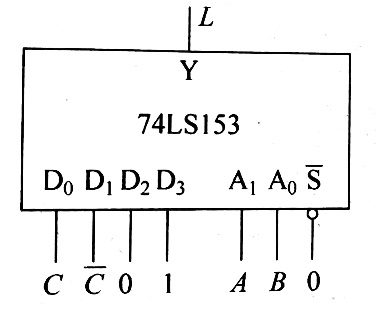

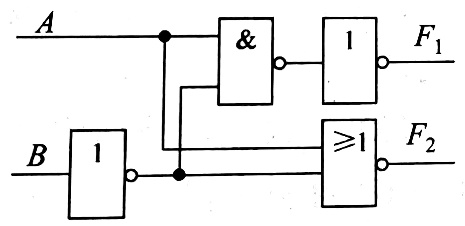

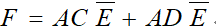

- 试用数据选择器74LS153实现逻辑函数

,则按照如下电路设计,可以实现该逻辑函数的功能。

,则按照如下电路设计,可以实现该逻辑函数的功能。 ( )

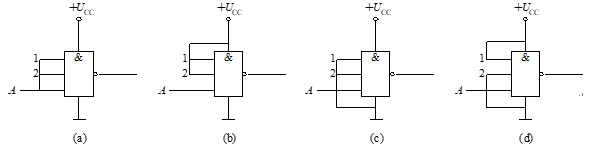

( ) - 如题图

所示电路中, TTL与非门输入端1、 2是多余的, 指出哪些接法是错误的( )。

所示电路中, TTL与非门输入端1、 2是多余的, 指出哪些接法是错误的( )。 - D触发器有以下哪几种功能?( )

- 基于硬件描述语言HDL的硬件设计主要特点是( )。

- 下列器件中,属于时序电路的有( )

- 一个四位二进制补码的表示范围是:( )

- 计算机系统中采用补码运算的目的是为了:( )

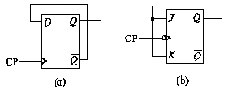

- 如图所示电路中,

CP脉冲的频率为2kHz,则输出端Q的频率为( )KHZ。

CP脉冲的频率为2kHz,则输出端Q的频率为( )KHZ。 - 8 位补码表示的定点整数的范围是:( )

- 进位计数制的两个基本要素是: ( )

- 一个字长为7位的无符号二进制整数能表示的十进制数值范围是: ( )

- 设任意一个十进制整数为 D,转换成二进制数为 B。根据数制的概念,下列叙述中正确的是:( )

- 下列数中最小的数是:( )

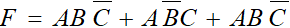

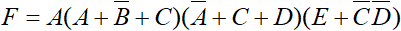

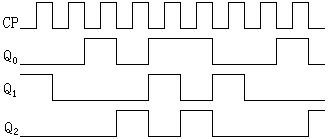

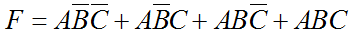

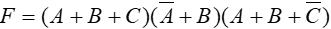

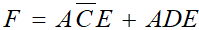

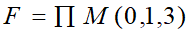

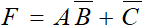

- 逻辑函数

的最简“与-或”表达式为( )

的最简“与-或”表达式为( ) - 逻辑函数

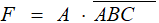

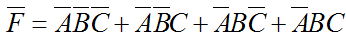

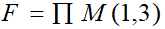

的最大项之积表达式为( )

的最大项之积表达式为( ) - 十进制数 91 转换成二进制数是: ( )

- -51转化为补码为:( )

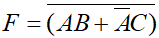

- 下图

所示电路的逻辑功能是: ( )

所示电路的逻辑功能是: ( ) - 现代计算机中采用二进制数制是因为二进制数的优点是:( )

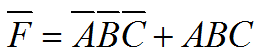

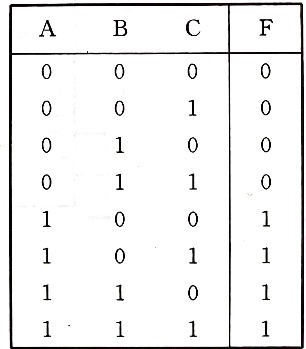

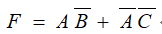

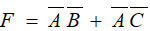

- 设计一个不一致电路,当A,B,C三个输入不一致时,输出F为1;一致时输出F为0,(1)

(2)

(2) 写出逻辑函数表达式( )

写出逻辑函数表达式( ) - 在机器数中,什么码的零表示形式是惟一的?( )

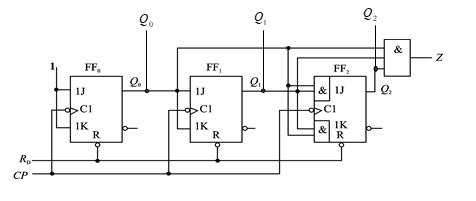

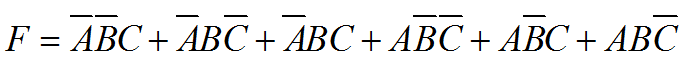

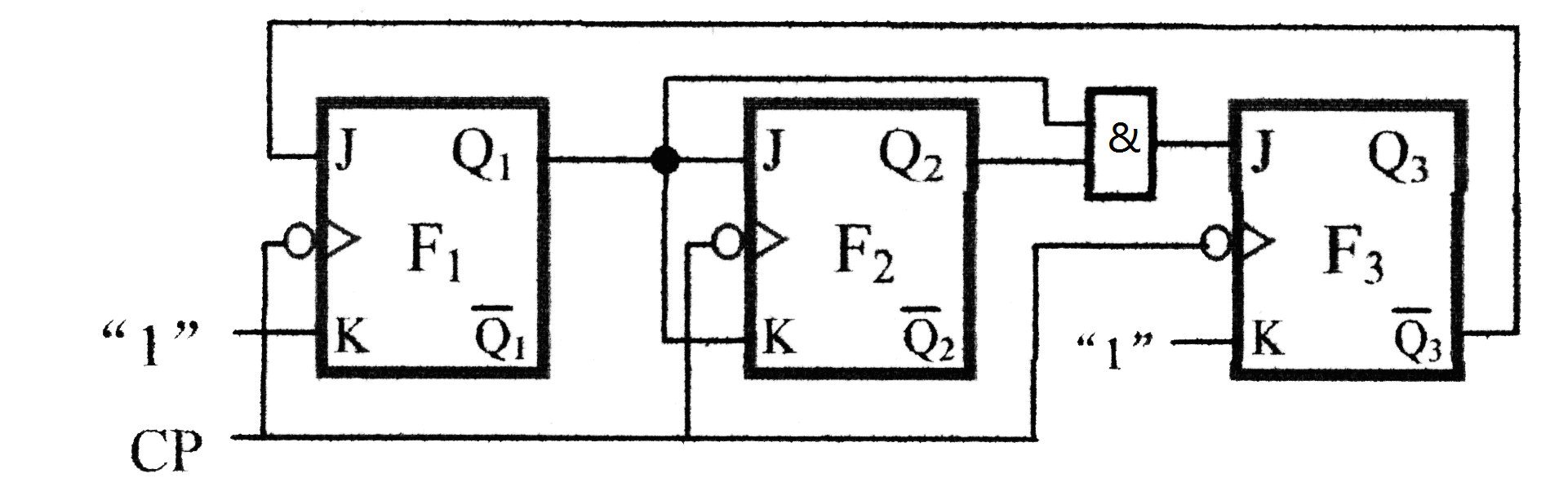

试分析题图

所示电路,说明它是多少进制计数器,采用了何种进位方式。( )

所示电路,说明它是多少进制计数器,采用了何种进位方式。( )- 如果 X 为负数,由 [x]补求[-x]补是将:( )

- FPGA是采用( )技术实现互联的。

- 以下哪项是FPGA不同于其他PLD结构的设计特点( )。

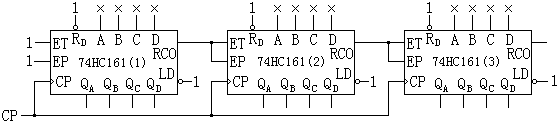

- 在某计数器的输出端观察到如图

所示的波形,试确定该计数器的模。( )

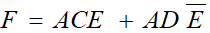

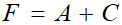

所示的波形,试确定该计数器的模。( ) - 逻辑函数

的最简“与-或”表达式为( )

的最简“与-或”表达式为( ) - 下图电路

的功能是? ( )

的功能是? ( ) - 函数

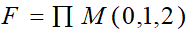

的最简与或式为( )。

的最简与或式为( )。 - https://image.zhihuishu.com/zhs/doctrans/docx2html/202103/a6ebcb445ebd4741a16ffe8cd8204c5a.png

- 根据如图所示电路,

针对A,B的输入,存在输出结果:

(1)A>B,F1F2=10;

(2)A<B,F1F2=01;

(3)A=B,F1F2=00;

则分析电路功能可知( ) - 根据如下真值表,

(1)

(2) 写出的逻辑函数表达式( )。

写出的逻辑函数表达式( )。 - 函数

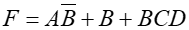

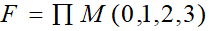

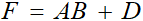

的最简与或式为( )。

的最简与或式为( )。 - 函数

的最简与或式为( )。

的最简与或式为( )。 - 已知A=(10111110)2 , B=(AE)16, C=(184)10, 关系成立的不等式是:( )

A:错 B:对

答案:错

A:错 B:对

答案:错

A:对 B:错

答案:对

A:对 B:错

答案:错

A:对 B:错

答案:对

A:对 B:错

答案:对

A:对 B:错

答案:

A:对 B:错

答案:对

A:对 B:错

答案:B:错

A:错 B:对

A:错 B:对

A:错 B:对

A:错 B:对

A:错 B:对

A:图(c)

B:图(d)

C:图(a)

D:图(b)

A:置1

B:翻转

C:其余都不对

D:保持

E:置0

A:主要设计文件是用HDL语言编写的源程序

B:IP的使用合嵌入式模块的应用

C:自上而下的设计方法

D:降低了设计难度

A:其余都不对

B:寄存器和比较器

C:计数器和全加器

D:计数器和寄存器

E:全加器和比较器

A:0~15

B:-7~8

C:-7~7

D:-8~7

A:提高运算速度

B:与手工运算方式保持一致

C:提高运算的精度

D:简化计算机的设计

A:6kHz

B:1kHz

C:4kHz

D:2kHz

A:-127~+127

B:-128~ +128

C:-128 ~+127

D:-127 ~+128

A:阶码和尾码

B:整数和小数

C:基数和权

D:定点数和浮点数

A:0~255

B:0~128

C:0~127

D:0~256

A:数字 B的位数≥数字 D的位数

B:数字 B的位数 >数字 D的位数

C:数字 B的位数 <数字D 的位数

D:数字 B的位数≤数字 D的位数

A:[10010101]反

B:[10010101]补

C:[10010101]2

D:[10010101]原

A:

B:

C:

D:

A:

B:

C:

D:

A:1011011

B:1001101

C:1011101

D:10101101

A:10001101

B:11001101

C:11001100

D:10110011

A:其余都不对

B:是一个3位二进制(模八)同步加法计数器

C:是一个3位二进制(模六)同步加法计数器

D:是一个3位二进制(模三)同步加法计数器

A:物理上容易实现且简单可靠;运算规则简单;适合逻辑运算。

B:只有0,1两个符号,容易书写

C:代码表示简短,易读

D:容易阅读,不易出错

A:仅表达式2正确

B:表达式1和2全部错误

C:表达式1和2全部正确

D:仅表达式1正确

A:补码

B:反码

C:原码和反码

D:原码

A:其余都不对

B:4096,采用并行进位方式

C:256,采用并行进位方式

D:4096,采用串行进位方式

E:256,采用串行进位方式

A:[x]补各值保持不变

B:[x]补符号位变反,其他各位不变

C:[x]补连同符号位一起各位变反,末位加 1

D:[x]补除符号位外,各位变反,末位加 1

A:SRAM

B:熔丝

C:EECMOS

D:CMOS

A:在PAL基础上开发通用阵列逻辑器件

B:在GAL基础上增大了集成度规模

C:基于乘积项的可编程结构,由可编程的与阵列和固定的或项组成

D:基于编程的查找表LUT结构,依靠连接点合理配置

A:模为7

B:模为6

C:模为5

D:模为8

A:

B:

C:

D:

A:模为7的加1计数器

B:模为5的加1计数器

C:其余都不对

D:模为8的加1计数器

A:

B:

C:

D:

A:

B:

C:

D:

A:全部正确

B:仅(2)正确

C:仅(3)正确

D:仅(1)正确

A:逻辑函数表达式1和2全部正确

B:仅逻辑函数表达式2正确

C:逻辑函数表达式1和2全部错误

D:仅逻辑函数表达式1正确

A:

B:

C:

D:

A:

B:

C:

D:

A:C<B<A

B:B<C<A

C:A<B<C

D:B<A<C

温馨提示支付 ¥5.00 元后可查看付费内容,请先翻页预览!