第三章单元测试

比较常用硬件描述语言有( )

VHDL对设计的描述具有相对独立性,因此设计者可以不懂硬件的结构,也不必管最终设计的目标器件是什么。

对于VHDL的编译器和综合器来说,程序文字的大小写是不加区分的。

VHDL作为一种硬件描述语言,其所有语句经过逻辑综合后都会变成对应的硬件电路。

下列数制基数表示的文字中表示十六进制数的是( )

在下标段的定义中,TO表示数组下标序列由低到高,,而DOWNTO表示数组下标序列由高到低。

虽然VHDL仿真器允许变量和信号设置初始值,但在实际应用中,VHDL综合器并不会把这些信息综合进去。

从硬件电路系统来看,( )相当于当前层次中各模块之间的连线以及上面的值。

信号的使用和定义范围是实体、进程、子程序、结构体和程序包。

STD_LOGIC_VECTOR数据类型的数据对象赋值的原则是:同位宽、同数据类型的矢量间才能进行赋值。

由于标准逻辑位数据类型的多值性,在条件语句中,如果未考虑到STD_LOGIC的所有可能的取值情况,综合器可能会插入不希望的锁存器。

对于数据类型不同的参量需要进行相互作用和传递时,首先必须进行数据类型的转换,这是因为VHDL是一种强类型语言,要求各种数据类型相同的参量,才能相互作用和传递。

类型转换函数方式,就是通过定义一个数据类型转换函数,将属于某种数据类型的数据对象转换成属于另一种数据类型的数据对象。

VHDL语言操作符的种类包括( )

下列符号中表示逻辑左移的是( )

下列属于变量赋值的特点的是( )

信号赋值目标 := 赋值源;其中冒号加等号(:=)作为一个整体,称之为信号赋值符号。

变量赋值目标<= 赋值源;其中指向左边的双箭头(<=)作为一个整体,称之为变量赋值符号。

下列不属于顺序语句的是( )

下列属于转向控制语句的是( )

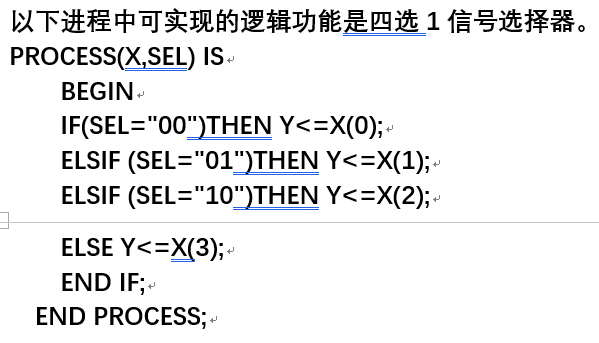

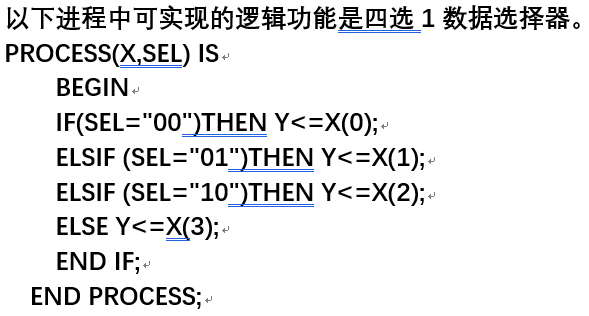

IF语句是一种条件语句,它根据语句中所设置的一种或多种条件,有选择地执行指定的顺序语句。

CASE选择句中的“=>”不是操作符,它相当于“THEN”的作用。

LOOP循环语句的循环方式由( )语句控制。

一般情况下,只有WAIT UNTIL格式的等待语句可以被综合器接受。

敏感信号等待语句是指( )

条件等待语句是指( )

VHDL中可以具有属性的项目有( )

下列属于顺序语句的是( )

下列属于并行语句的是( )

进程经综合后对应的硬件电路,对进程中的所有可读入信号都是敏感的,而在VHDL行为仿真中并非如此,除非将所有的读入信号列为敏感信号。

选择信号赋值语句允许有条件重叠的现象,也允许存在条件涵盖不全情况。

选择信号赋值语句本身不能在进程中应用,但其功能却与进程中的CASE语句的功能相似。

VHDL元件例化端口映射语句“ U1:ND2 PORT MAP(S1,S2,C=>Z1);”中的端口映射关联方式为( )

VHDL元件例化端口映射名字关联方式的符号为( )

VHDL的元件例化语句用于建立端口之间映射关系的常用方式( )

对于内部由多个规则模块构成而两端结构不规则的电路,可以用FOR_GENERATE语句来描述电路内部的规则部分,而根据电路两端的不规则部分形成的条件用IF_GENERATE语句来描述。

VHDL子程序调用的特点有( )

VHDL的函数首由( )组成。

一般地,可在过程定义参量表可以定义的数据流向模式有( )

一个程序包应包含常数说明、数据类型说明、元件定义、子程序说明等四种内容。

对于没有子程序说明的程序包体可以省去,因此程序包首可以独立定义和使用。

VHDL的描述风格有三种,分别是( )

在VHDL的结构体中只描述了所希望电路的功能或者说电路行为,而没有直接指明或涉及实现这些行为的硬件结构的描述方式称为( )

译码器可以用于( )

三态门电路的输出值包括( )

触发器和寄存器(锁存器),都是具有存储功能的电路,其VHDL程序设计的基本方法是相同的。

计数器的设计,其基本功能包括计数控制和进位控制。其中计数控制又分为正常计数和边界处理,正常计数是进行加1操作或加N操作;边界处理则进行清零。

所谓分频电路,就是将一个给定的频率较高的数字输入信号,经过适当的处理后,产生一个或数个频率较低的数字输出信号。

有关FIFO正确的说法是( )

作为FIFO的设计,它包括数据的写操作、数据的写地址修改、数据写满控制,数据的读操作、数据的读地址修改、数据读空控制,因此可用6个进程来描述对应的操作。

进程间一般是顺序运行的,但由于敏感信号的设置不同以及电路的延迟,在时序上,进程间的动作是没有先后顺序的。

进程间一般是并行运行的,但由于敏感信号的设置不同以及电路的延迟,在时序上,进程间的动作是有先后顺序的。

A:ABEL B:VHDL C:Verilog HDL D:C++

答案:ABEL###VHDL###Verilog HDL

A:对 B:错

A:对 B:错

A:对 B:错

A:2#1111_1110# B:16#E#E1 C:10#16#

A:错 B:对

A:错 B:对

A:常量 B:信号 C:变量

A:对 B:错

A:错 B:对

A:对 B:错

A:对 B:错

A:错 B:对

A:关系操作符 B:算术操作符 C:符号操作符 D:逻辑操作符

A:MOD B:SLL C:SRL D:ROL

A:具有局部特征 B:赋值过程总是有某种延时 C:具有全局性特征 D:赋值过程立即发生

A:错 B:对

A:对 B:错

A:CASE选择语句 B:变量赋值语句 C:进程语句 D:LOOP循环语句

A:WAIT语句 B:LOOP循环语句 C:IF条件语句 D:CASE选择语句

A:错 B:对

A:对 B:错

A:WAIT B:NEXT C:CASE D:EXIT

A:对 B:错

A:WAIT UNTIL条件表达式 B:WAIT语句 C:WAIT ON 信号表

A:WAIT UNTIL条件表达式 B:WAIT语句 C:WAIT ON 信号表

A:信号、变量、常量 B:类型、子类型 C:实体、结构体、配置、程序包 D:过程、函数

A:断言(ASSERT)语句 B:进程语句 C:报告(REPORT)语句 D:决断(RESOLUTION)函数语句

A:并行信号赋值语句 B:条件信号赋值语句 C:进程语句 D:LOOP循环语句

A:错 B:对

A:对 B:错

A:对 B:错

A:位置关联 B:名字关联 C:混合关联 D:结构关联

A:== B:>= C:=> D:=

A:混合关联 B:名字关联 C:位置关联 D:结构关联

A:对 B:错

A:从硬件角度讲,一个子程序的调用类似于一个元件模块的例化 B:在进程中允许对子程序进行调用 C:可以在结构体或程序包中的任何位置对子程序进行调用 D:在进程中不允许对子程序进行调用

A:函数名 B:参数表 C:数据类型 D:函数体

A:IN B:OUTPUT C:INOUT D:OUT E:INPUT

A:错 B:对

A:错 B:对

A:行为描述 B:数据流描述 C:结构描述 D:门电路描述

A:RTL描述 B:行为描述 C:结构描述

A:控制译码 B:地址译码 C:显示驱动译码 D:指令译码

A:错 B:对

A:对 B:错

A:高电平 B:高阻态 C:低阻态 D:低电平

A:对 B:错

A:错 B:对

A:错 B:对

A:FIFO,本质上是一个读写存储器,但它的存储规律是先进先出 B:FIFO,本质上是一个读写存储器,但它的存储规律是后进先出 C:FIFO,本质上是一个读写存储器,但它的存储规律是先进后出

A:错 B:对

A:错 B:对

A:对 B:错