第四章单元测试

多位加法器的构成有两种方式:并行进位和串行进位。其中并行进位方式设有进位产生逻辑,运算速度较快;串行进位方式是将全加器级联构成多位加法器,运行速度较慢。

对于组合逻辑程序,在进行VHDL程序的时序仿真的时候,不论每组测试数据的持续时间的长短,都能得到正确的结果。

对于相同的一个VHDL设计,不管采用什么样的FPGA芯片来实现,该系统的最高频率是相同的。

对于相同的一个VHDL设计,若采用不同的FPGA芯片来实现,该系统的最高频率可能会是不同的。

语句“IF LD='1' THEN COUNT<=D;”是一个计数器控制进程中的一个语句,其中COUNT为保存计数过程中间结果的信号,则该语句的作用是( )

元件例化语句中的端口映射语句“U1: LCNT8 PORT MAP(CLK=>CLK, LD=>LD1, D=>A, CAO=>CAO1); ”,其端口映射方式是( )

在CORDIC算法的硬件实现方案中,相对于迭代结构,流水线结构的优点有( )

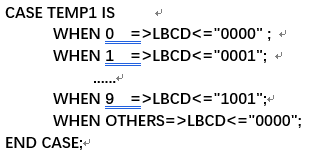

若TEMP1为10以内的正整数,下述以CASE TEMP1开始的选择语句的功能是( )

一个可进行硬件验证的完整的SOBEL图像边缘检测器包括的模块有( )

一个完整的SOBEL图像边缘检测器,其中求出四个方向的图像梯度数据绝对值的最大值,同时判别最大值出现的方向的模块是( )

A:对 B:错

答案:对

A:错 B:对

A:错 B:对

A:对 B:错

A:高电平预置数 B:低电平预置数 C:中电平预置数

A:位置关联方式 B:名字关联方式 C:混合关联方式

A:控制比较简单 B:控制比较复杂 C:硬件开销很小 D:处理速度非常快

A:将10以内的正整数TEMP1进行显示驱动译码,并将译码结果赋值给LBCD B:将10以内的正整数TEMP1转换成四位二进制数BCD编码,并赋值给LBCD C:将10以内的正整数TEMP1进行显示数据选择,并将选择结果赋值给LBCD

A:数据处理模块(PROCESSOR) B:像素窗口刷新模块(REFRESH) C:图像数据(模拟)采集模块(MINPUT) D:数据显示处理模块(DISPLAY) E:串入并出模块(SIPO) F:帧窗口接收模块(FIFO)

A:像素窗口刷新模块(REFRESH) B:串入并出模块(SIPO) C:帧窗口接收模块(FIFO) D:数据处理模块(PROCESSOR)

温馨提示支付 ¥3.00 元后可查看付费内容,请先翻页预览!