第十章单元测试

- Moore类型的有限状态机的输出不仅取决于当前的状态,还与当前的输入有关。( )

- 有限状态机是由寄存器组和组合逻辑构成的硬件时序电路。( )

- 有限状态机描述的步骤包括:

①模块定义和输入输出端口声明; ②编写always语句;

③选择合适的状态编码; ④定义状态寄存器变量;

正确的描述顺序是( ) - 下列不属于有限状态机的优点的是( )

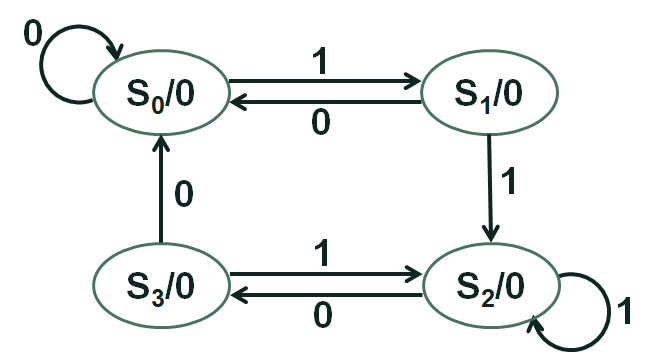

- 为了完成如下图所示的状态机:

在状态机的程序编写过程中,采用自然码编码和独热码编码,定义的状态寄存器变量的位宽通常分别为( )

A:错 B:对

答案:错

A:对 B:错

A:①③②④

B:①④③②

C:①②③④

D:①④②③

A:有限状态机设计方案相对固定,结构模式简单

B:在高速运算和控制方面,有限状态机比一般的CPU有优势

C:利用有限状态机设计的电路具有最佳的速度和功耗

D:有限状态机容易构成性能良好的同步时序逻辑模块

A:4位、4位

B:2位、4位

C:4位、5位

D:2位、5位

温馨提示支付 ¥3.00 元后可查看付费内容,请先翻页预览!